TC1796

System Units (Vol. 1 of 2)

Peripheral Control Processor (PCP)

User’s Manual 11-10 V2.0, 2007-07

PCP, V2.0

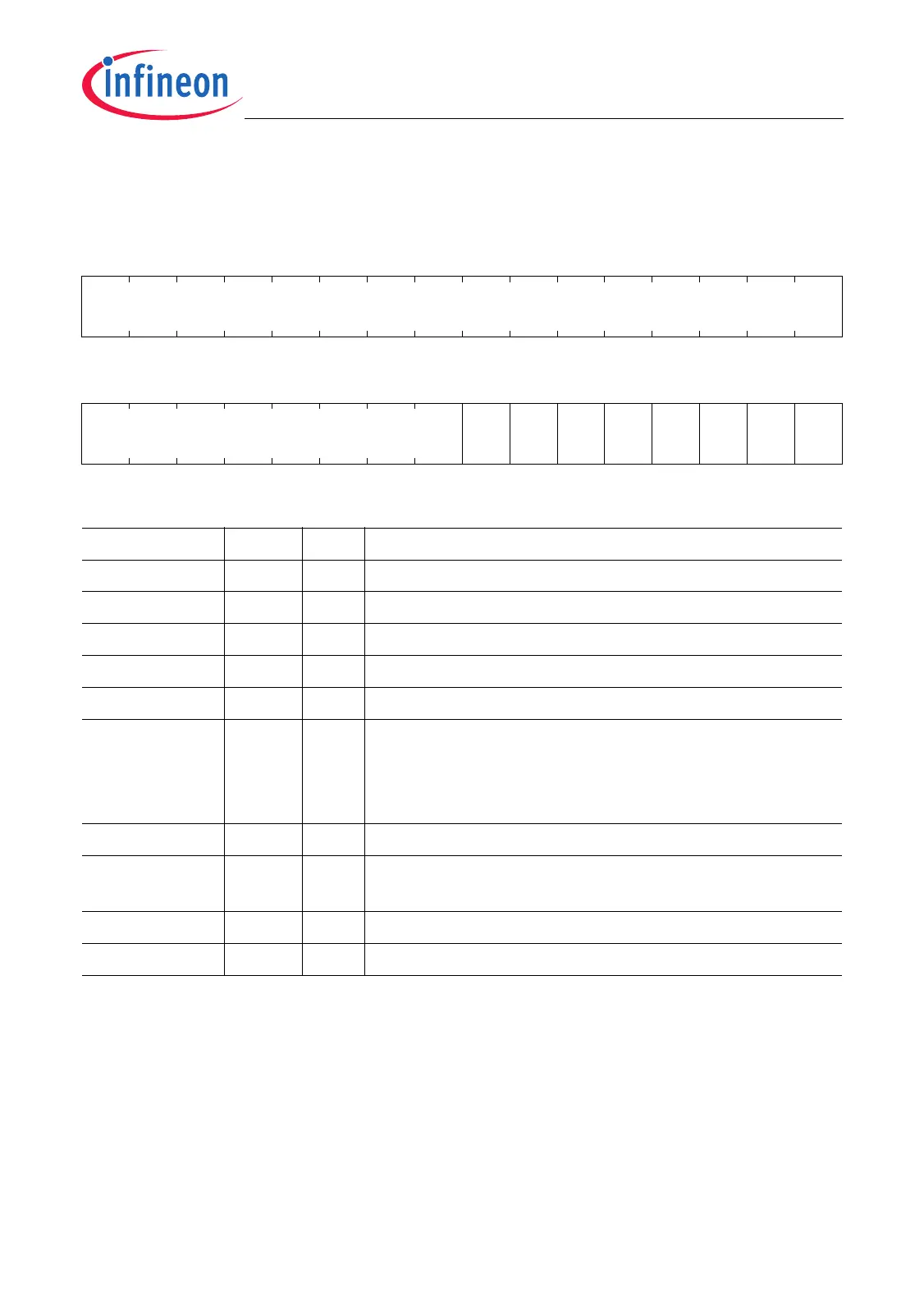

PCP Register R7

Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

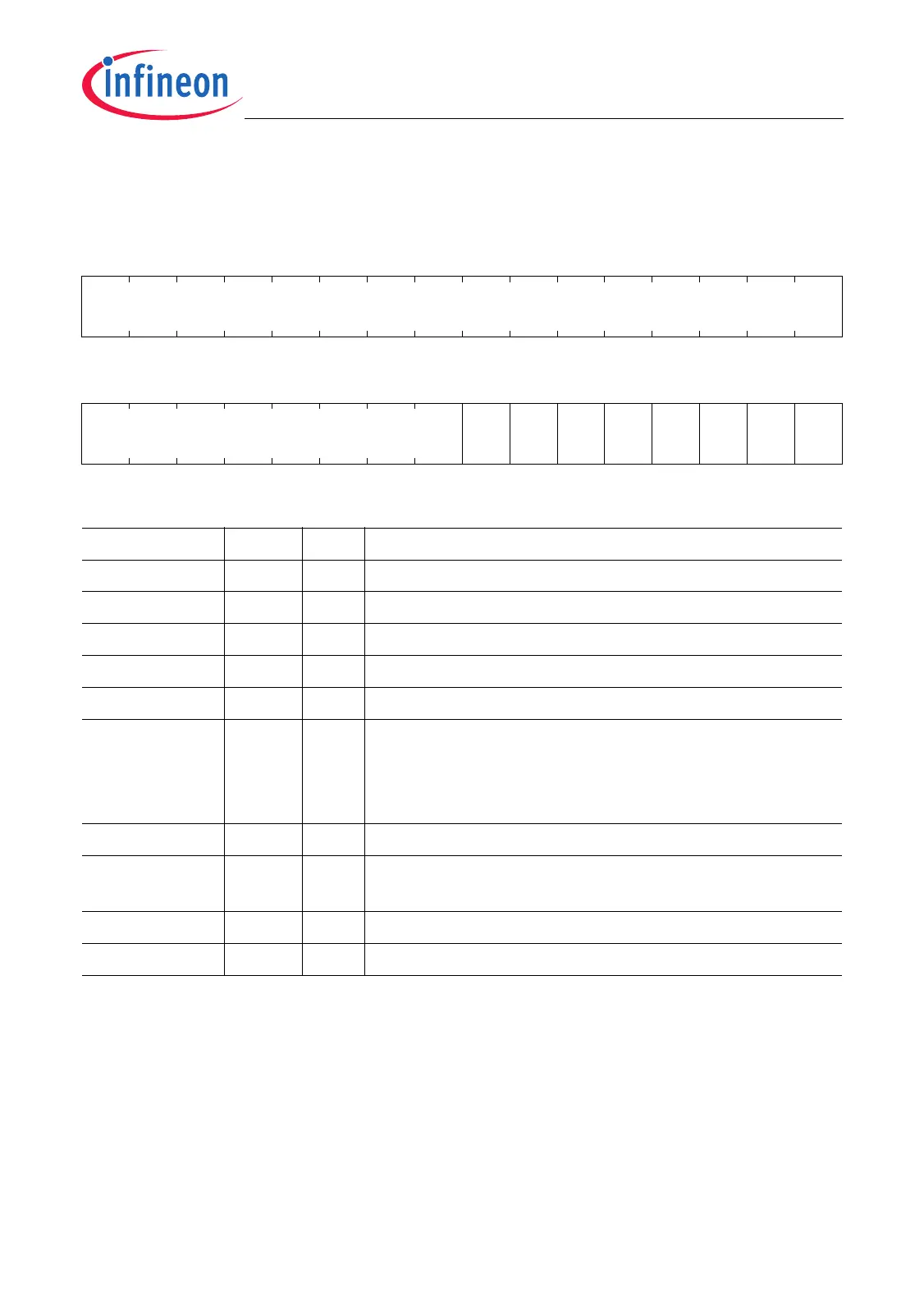

1514131211109876543210

DPTR – CEN IEN CNZ V C N Z

rw rw rw rw rw rw rw rw rw

Field Bits Type Description

Z 0rwZero

N 1rwNegative

C 2rwCarry

V 3rwOverflow

CNZ 4rwOuter Loop Counter 1 Zero Flag

IEN 5rwInterrupt Enable

0

B

Channel is not interruptible

1

B

Channel can be suspended in favor of a higher-

priority service request

CEN 6rwChannel Enable Control Bit

DPTR [15:8] rw Data Pointer Segment Address for PRAM

accesses

– 7rwReserved; should always be written with 0.

0 [31:16] r Reserved; read as 0; should be written with 0.

Loading...

Loading...