TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-14 V2.0, 2007-07

DMA, V2.0

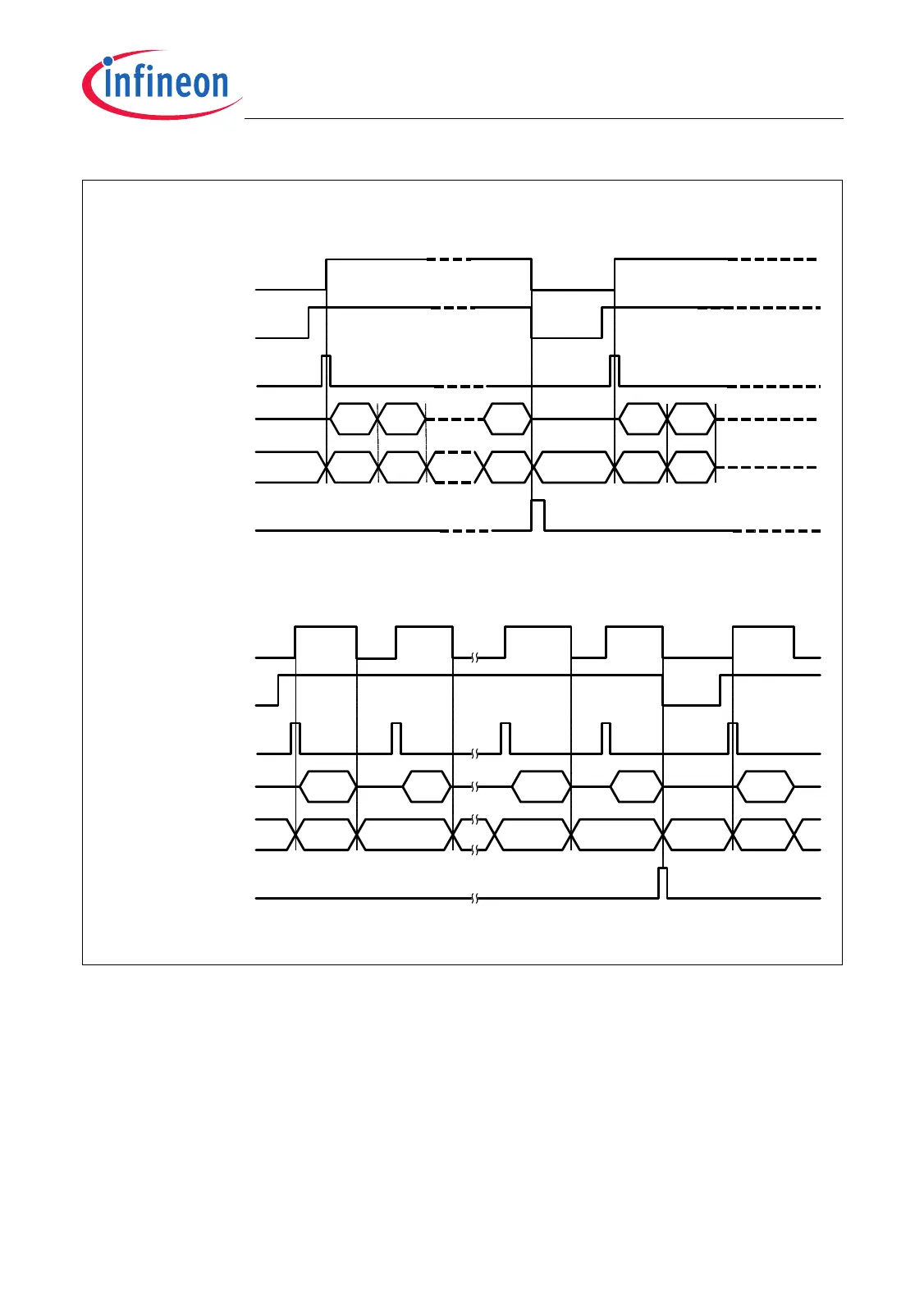

Figure 12-8 Hardware-controlled Single Mode Operation

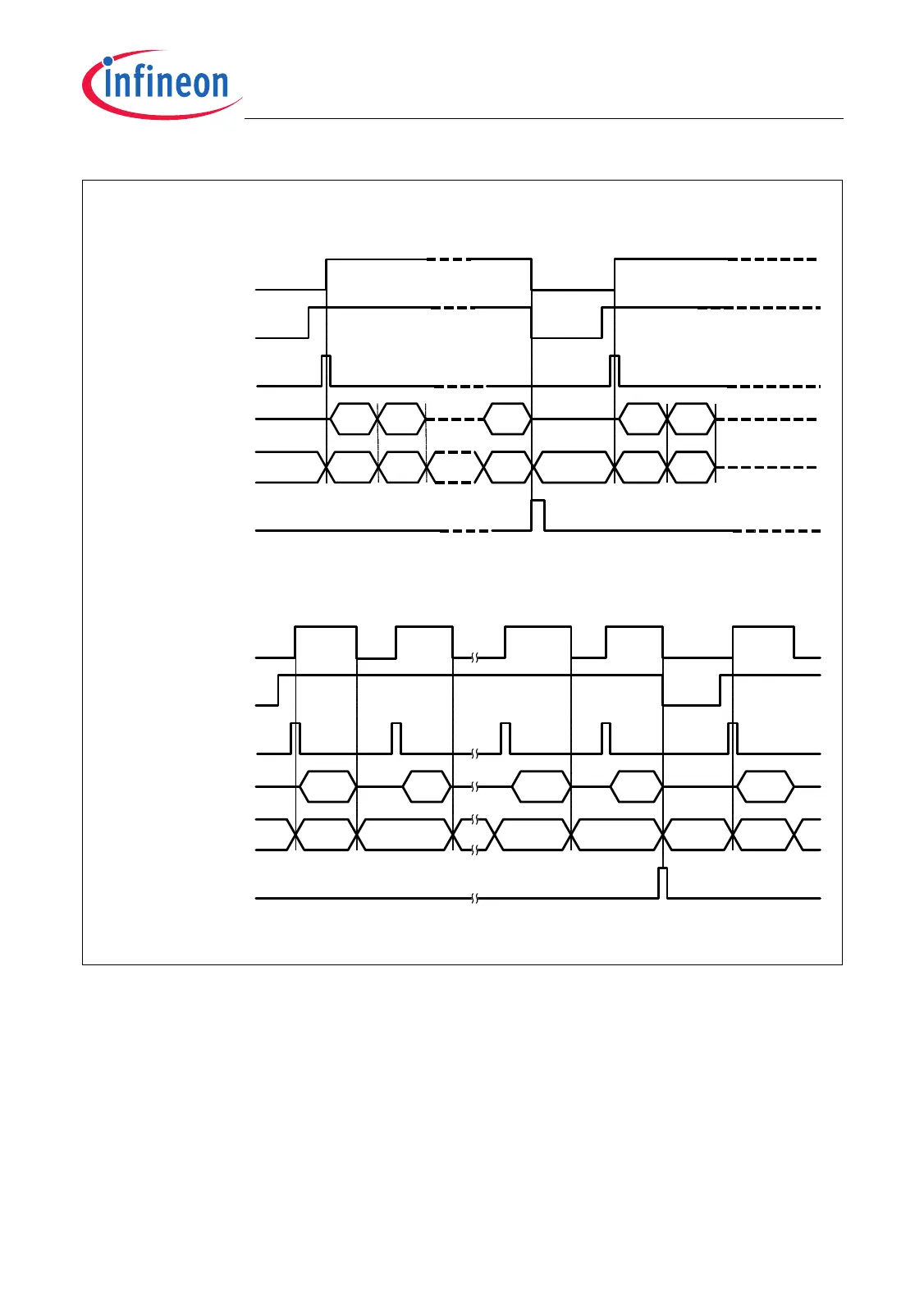

Hardware-controlled Continuous Mode

In hardware-controlled Continuous Mode (CHCRmn.CHMODE = 1), the hardware

transaction request enable bit HTREmn is not cleared at the end of a DMA transaction.

A new transaction of DMA channel mn with the parameters actually stored in the channel

register set of DMA channel mn is started each time when CHSRmn.TCOUNT reaches

000

H

. No software re-enable for a hardware request at CHmn_REQ is required.

MCT05687

tc = initial transfer count

tc = initial transfer count

CHCRmn.RROAT = 1

CHCRmn.RROAT = 0

TR0 TR1 TRn

tc-1

TR0 TR1

0tc tc-101 tc

TR0

tc-1tc

TR1

TRn-1 TRn

0 021 tc

TR0

TRSR.HTREmn

CHmn_REQ

INT

(triggered at the end

of a transaction with

IRDV = 0)

CHSRmn.TCOUNT

DMA Transfer mn

TRSR.CHmn

TRSR.HTREmn

CHmn_REQ

TRSR.CHmn

DMA Transfer mn

CHSRmn.TCOUNT

INT

(triggered at the end

of a transaction with

IRDV = 0)

Loading...

Loading...