TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-28 V2.0, 2007-07

DMA, V2.0

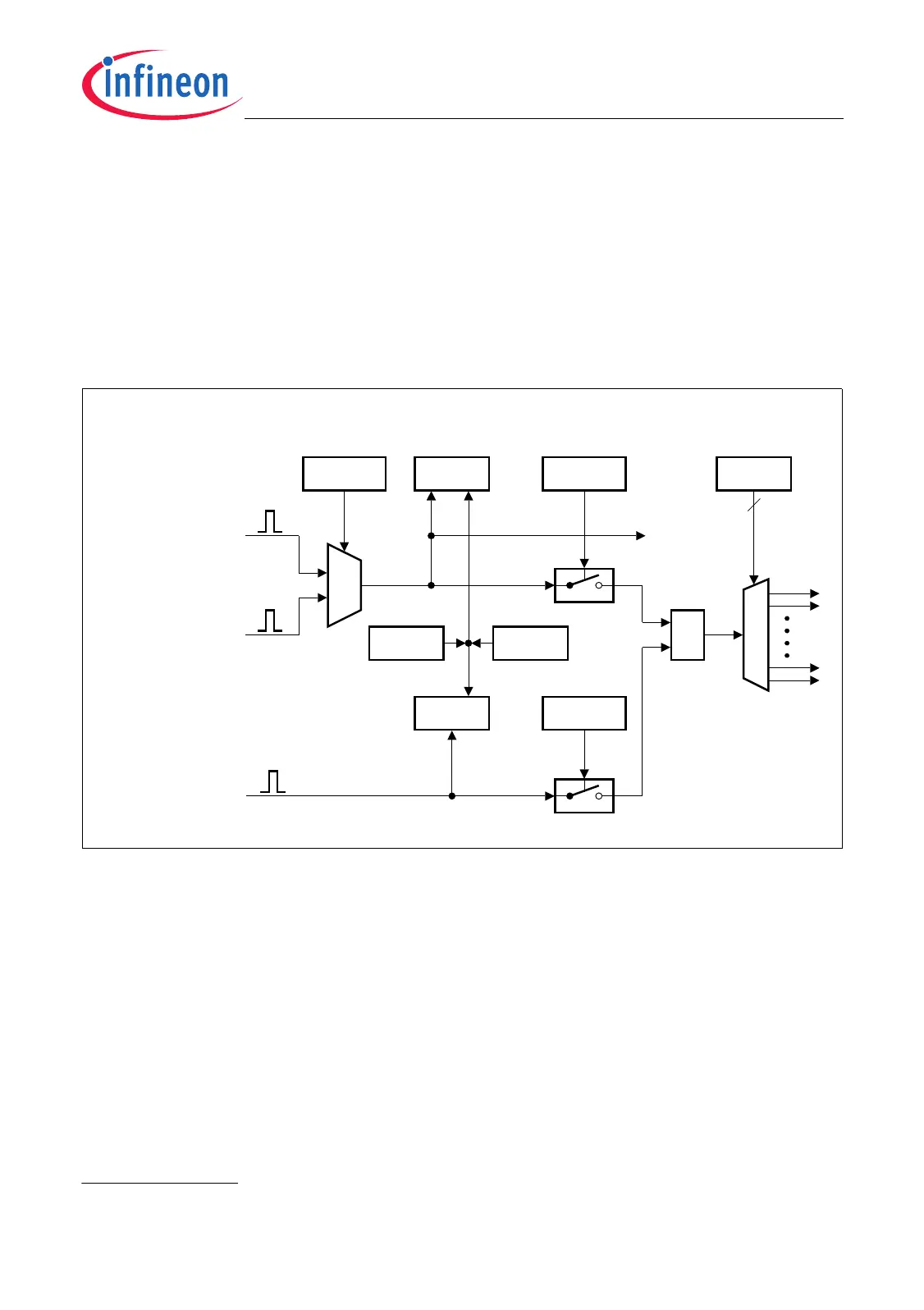

match interrupt is generated at the end of a DMA transaction (after the last DMA

transfer).

The pattern detection interrupt is indicated when status flag INTSR.IPMmn is set. The

status flags IPMmn and ICHmn can be cleared together by software when setting bit

INTCR.CICHmn (or CHRSTR.CHmn). The pattern detection interrupt of DMA channel

mn is enabled when bit CHICRmn.PATSEL is set to a value not equal to 00

B

. The

channel interrupt pointer CHICRmn.INTP determines which of the interrupt outputs

SR[15:0]

1)

will be activated on a pattern detection or channel interrupt.

Figure 12-19 Channel Interrupts

1) In the TC1796, only SR[7:0] are connected to interrupt nodes.

MCA05696_mod

CHSRmn.TCOUNT

Decremented

INTP

CHICRmn

INTCR

CHSRmn.TCOUNT

Matches with

CHICRmn.IRDV

4

ICHmn

INTSR

INTCT[0]

M

U

X

0

1

CHICRmn

INTCT[1]

CHICRmn

CICHmn

m = 0-1, n = 0- 7

Set

CHmn_OUT

Pattern Detection

Interrupt mn

PATSEL

CHCRmn

IPMmn

INTSR

Set

Clear

Clear

CHRSTR

CHmn

Enabled if

PATSEL ¹ 00

B

³1

Loading...

Loading...