TC1796

System Units (Vol. 1 of 2)

LMB External Bus Unit

User’s Manual 13-60 V2.0, 2007-07

EBU, V2.0

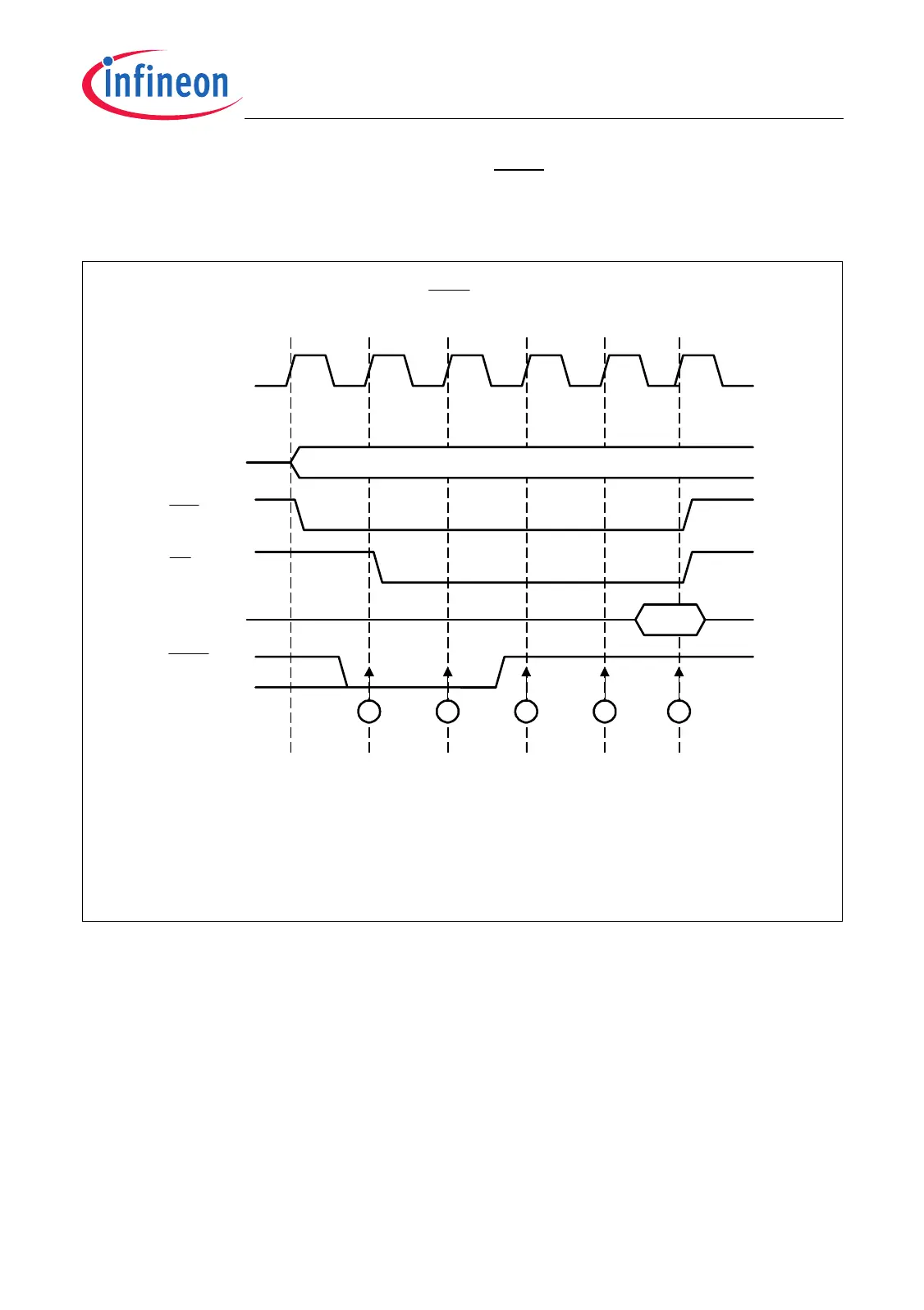

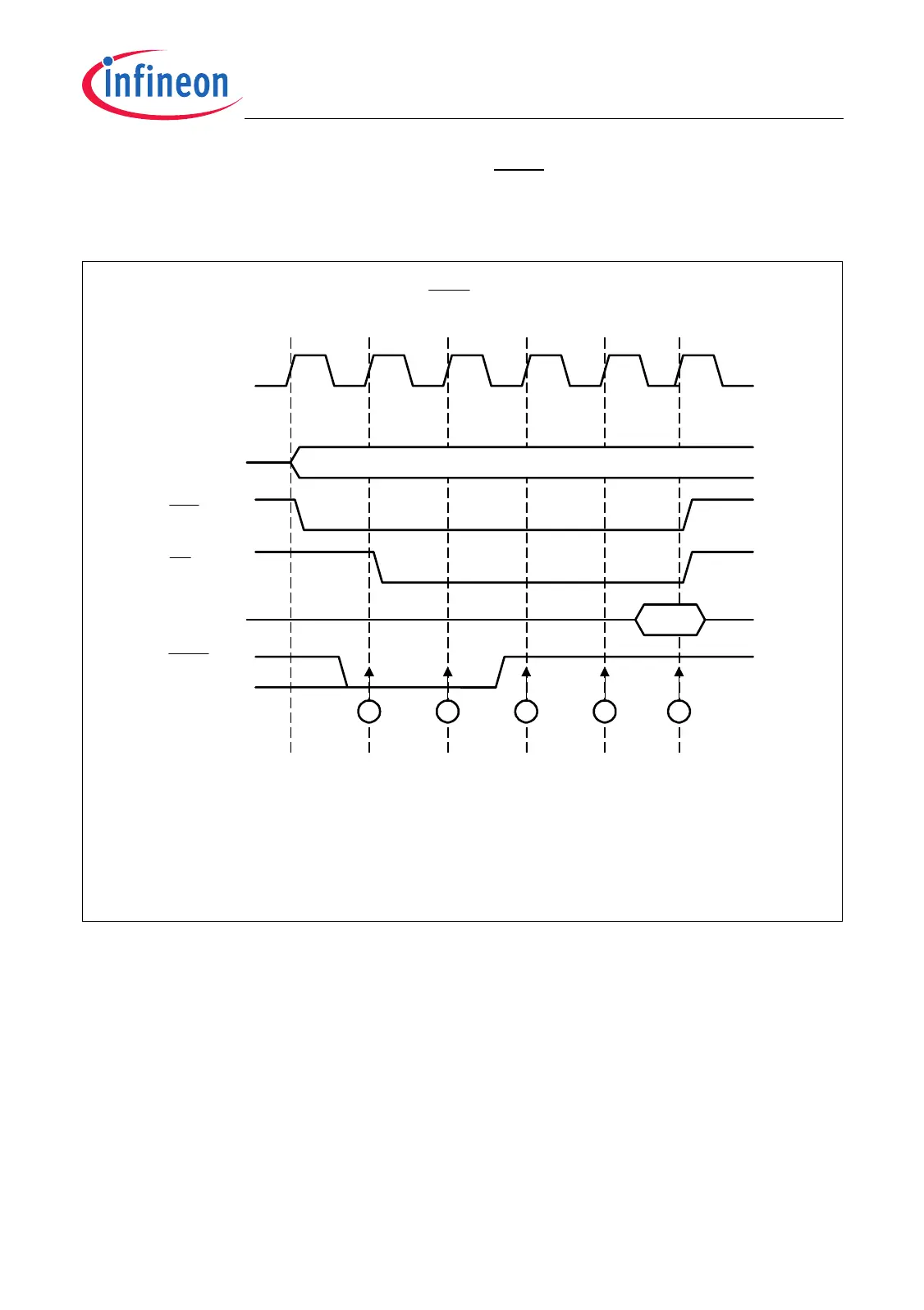

• Finally at LMBCLK edge 5, as a result of the WAIT input sampled as high at LMBCLK

edge 3, the EBU terminates the Command Phase, reads the input data from

D[31:0],and starts the Recovery Phase.

Figure 13-21 External Wait Insertion (Asynchronous Mode)

LMBCLK

A[23:0]

Address

MCT05732

AP CPi1 CPi2 CPe3 CPe4

CSx

RD

D[31:0]

RP1

Read Access with Asynchronous WAIT

1 2 3 4 5

Data in

In the example above, the Command Delay phase is internally

programmed to zero LMBCLK cycles (no Command Delay phase).

The Command Phase is internally programmed to two LMBCLK cycles.

All other phases are programmed for one LMBCLK cycle.

Note:

WAIT

(active low)

Loading...

Loading...