TC1796

System Units (Vol. 1 of 2)

LMB External Bus Unit

User’s Manual 13-105 V2.0, 2007-07

EBU, V2.0

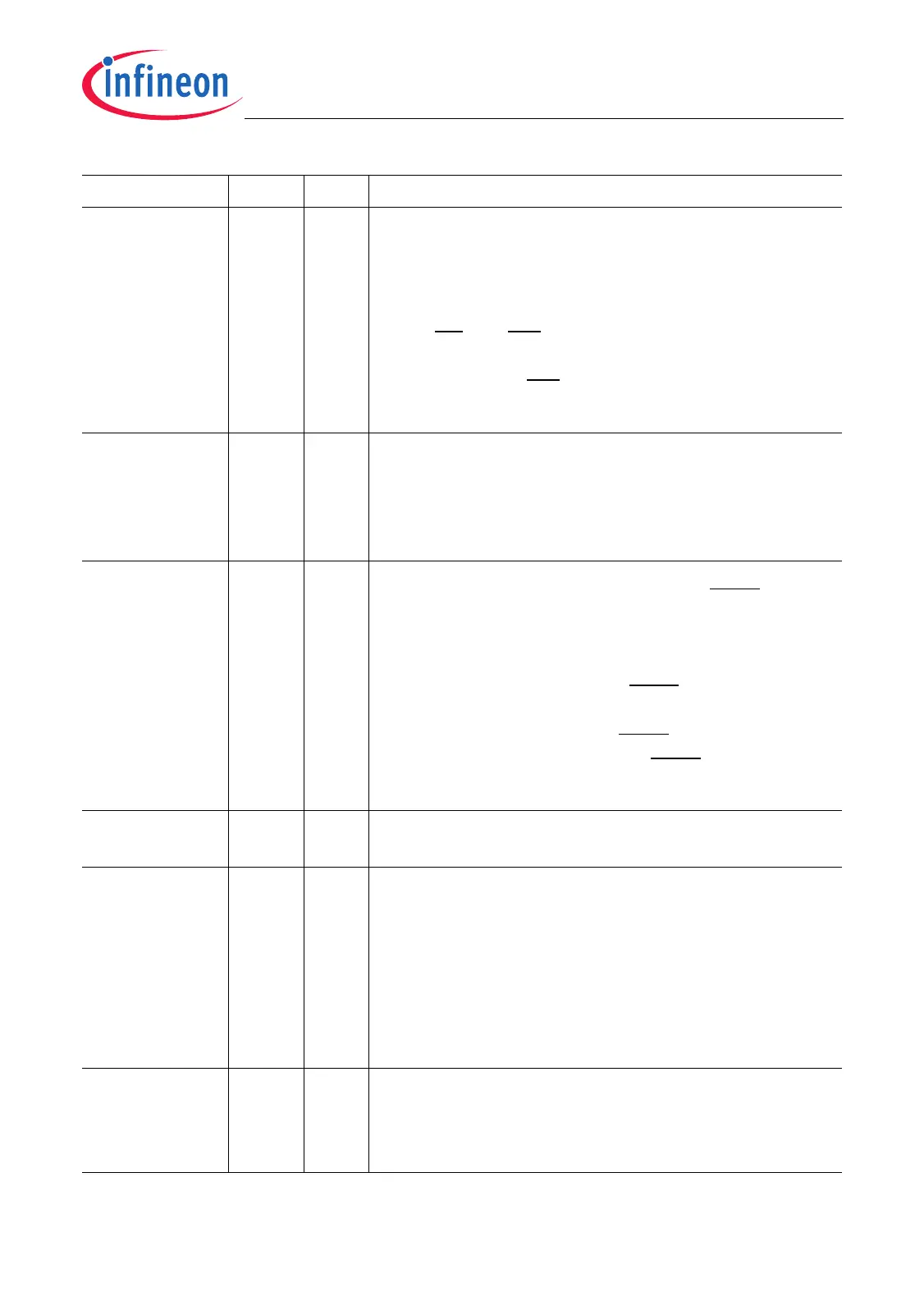

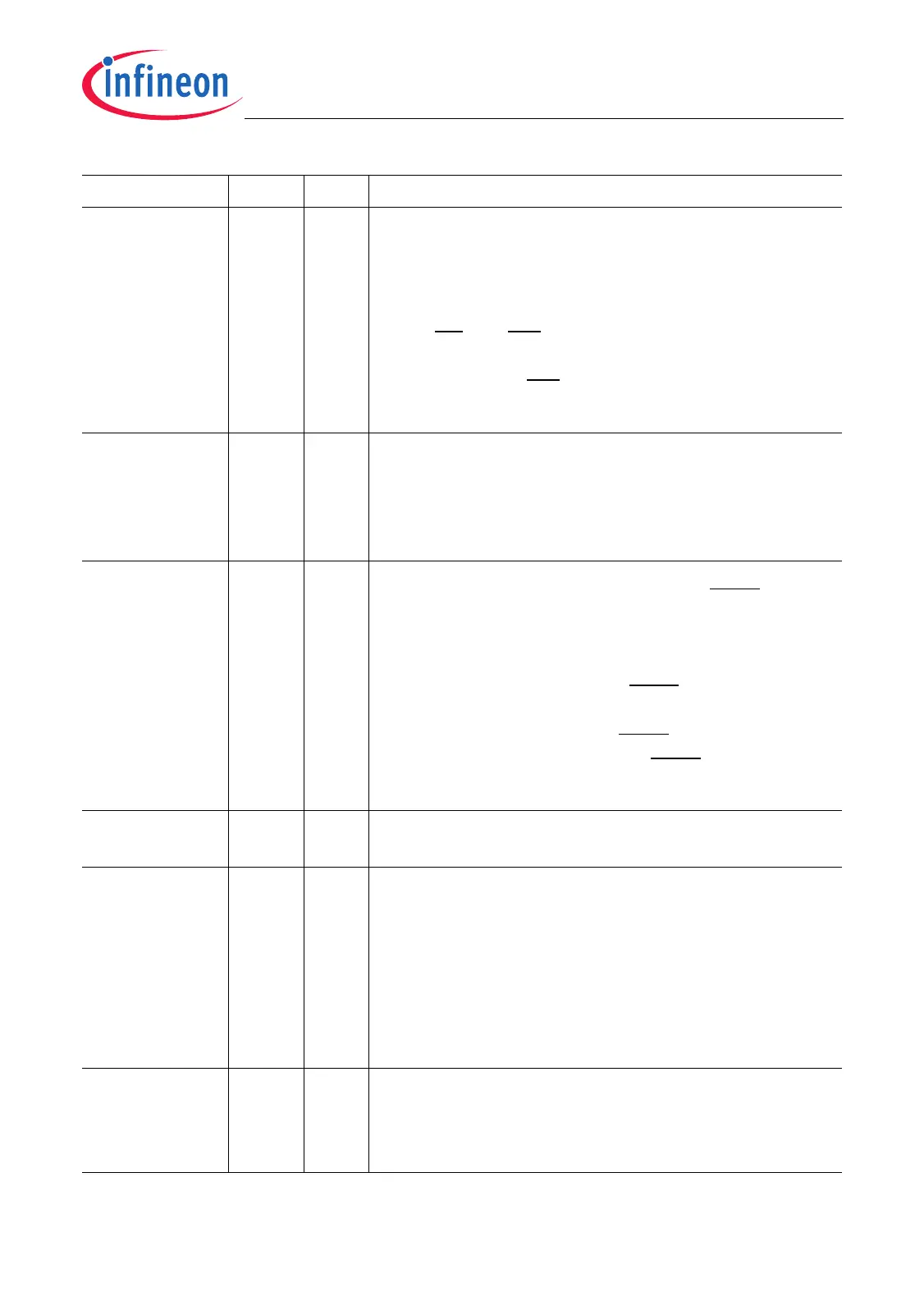

BCGEN [21:20] rw Byte Control Signal Control

This bit field selects the timing mode of the byte

control signals.

00

B

Byte control signals follow chip select timing.

01

B

Byte control signals follow control signal timing

(RD, RD/WR) (default after reset).

10

B

Byte control signals follow write enable signal

timing (RD/WR only).

11

B

Reserved.

PORTW [23:22] rw Port Width

00

B

Reserved.

01

B

16-bit.

10

B

32-bit (default after reset).

11

B

Reserved.

WAIT [25:24] rw External Wait State Control

This bit determines the function of the WAIT input.

This is specific to the device type (i.e. the AGEN

field).

00

B

OFF (default after reset).

01

B

Asynchronous input at WAIT (default after

reset).

10

B

Synchronous input at WAIT.

11

B

Data Handshake input at WAIT (Burst Flash

devices only).

0 [27:26] rw Reserved

Read as 0 after reset; must be always written with 0.

AGEN [30:28] rw Address Generation Control

This bit field selects the access type for the emulator

chip select region.

000

B

Demultiplexed (asynch.) access selected

(default after reset).

010

B

Burst Flash access selected.

Other values of AGEN are reserved and must not be

used!

WRITE 31 rw Memory Region Write Protection

0

B

Writes to the memory region are enabled

(default after reset).

1

B

Writes to the memory region are disabled.

Field Bits Type Description

Loading...

Loading...