TC1796

System Units (Vol. 1 of 2)

Interrupt System

User’s Manual 14-28 V2.0, 2007-07

Interrupt, V2.0

Note: The NMISR register is located in the address range of the System Control Unit

(see Page 5-61).

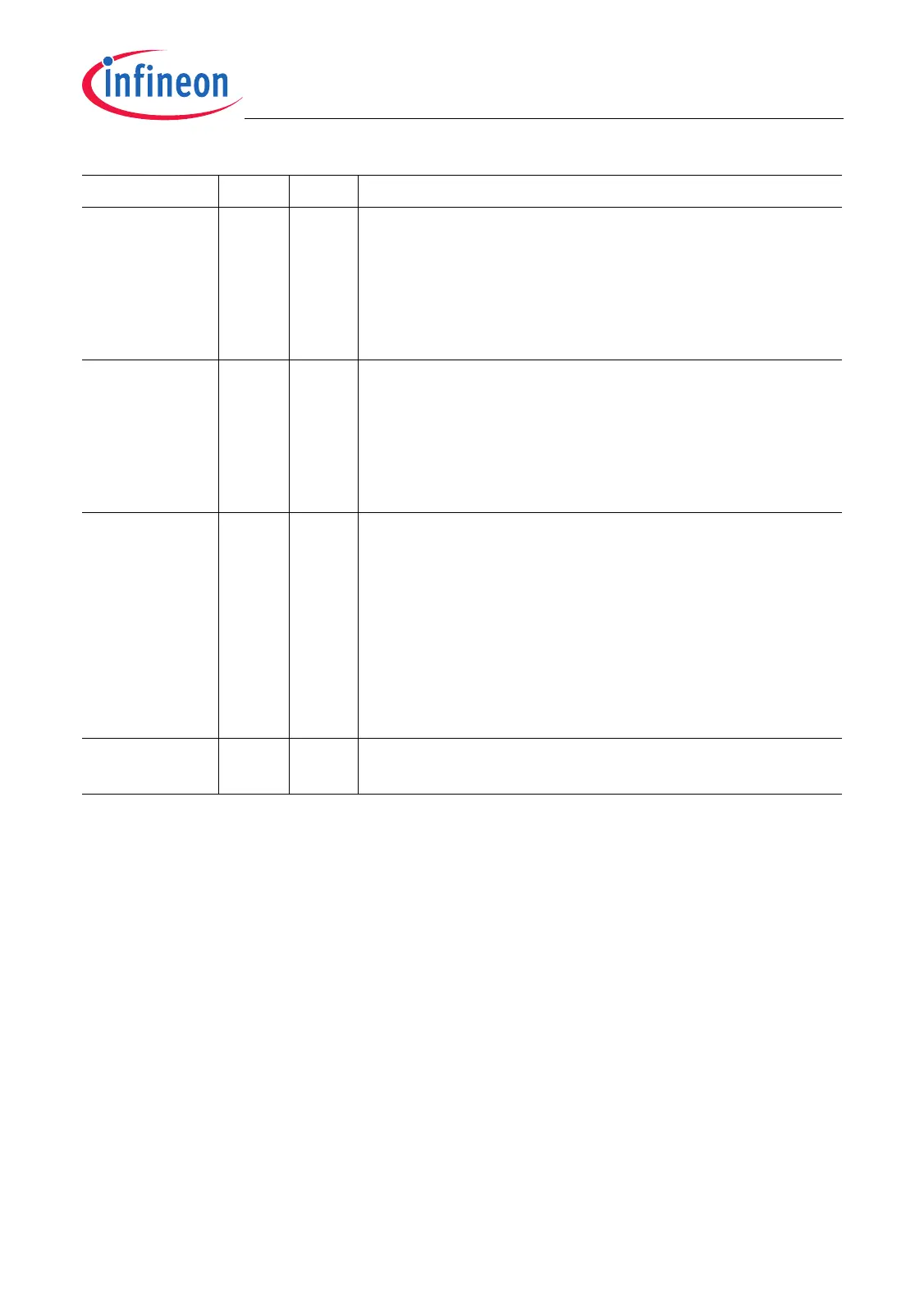

NMIPLL 1rhPLL NMI Flag

This flag indicates whether or not a PLL NMI request

has occurred.

0

B

No PLL NMI has occurred.

1

B

The PLL has lost the lock to the external crystal

(becomes unlocked).

NMIWDT 2rhWatchdog Timer NMI Flag

This flag indicates whether or not a Watchdog Timer

NMI request has occurred.

0

B

No watchdog NMI occurred.

1

B

The Watchdog Timer has entered the pre-

warning phase due to a watchdog error.

NMIPER 3rhParity Error NMI Flag

This flag indicates whether or not SRAM parity error

NMI request has occurred.

0

B

No SRAM parity error NMI occurred.

1

B

An SRAM parity error NMI has been detected.

The SRAM module where the parity error occurred can

be checked by reading SCU_PETSR.

NMIPER is only cleared with a NMISR read operation

when the bits in SCU_PETSR are no more set.

0 [31:4] r Reserved

Read as 0.

Field Bits Type Description

Loading...

Loading...