TC1796

System Units (Vol. 1 of 2)

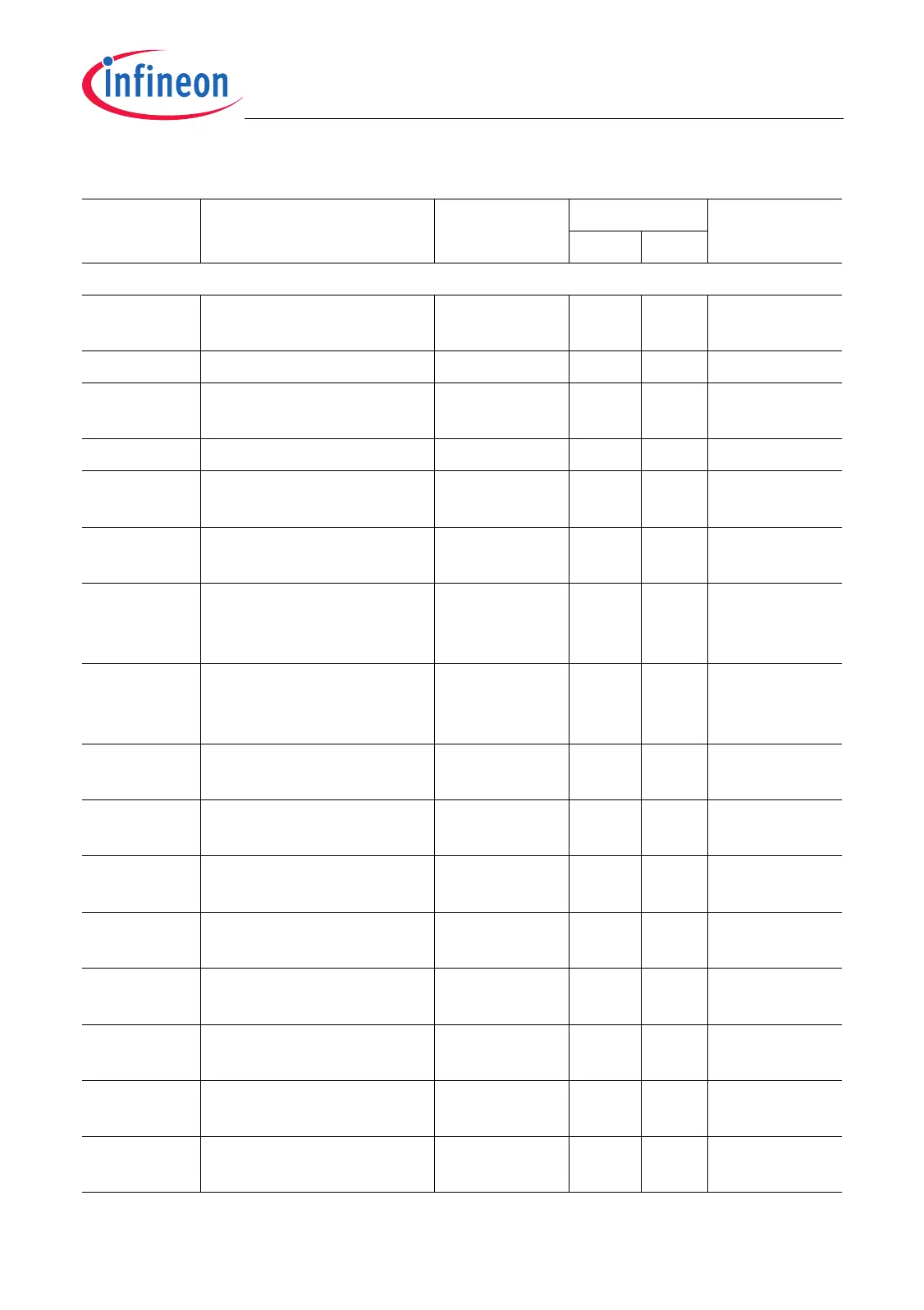

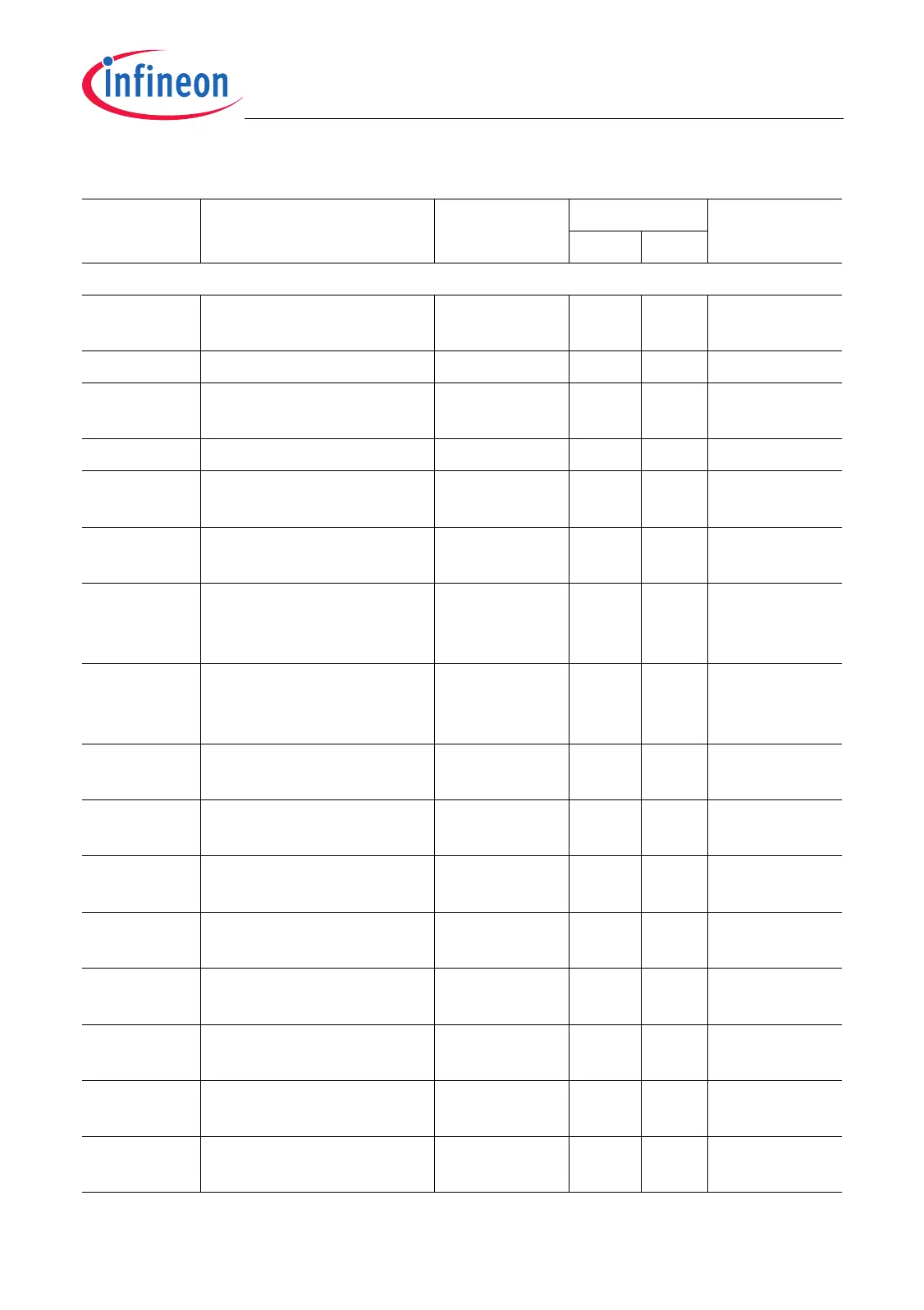

Register Overview

User’s Manual 18-53 V2.0, 2007-07

Regs, V2.0

Table 18-23 Address Map of DMA

Short Name Description Address Access Mode Reset Value

Read Write

Direct Memory Access Controller (DMA)

DMA_CLC DMA Clock Control

Register

F000 3C00

H

U, SV SV, E 0000 0000

H

– Reserved F000 3C04

H

nBE SV –

DMA_ID DMA Module

Identification Register

F000 3C08

H

U, SV BE 001A C0XX

H

– Reserved F000 3C0C

H

BE BE –

DMA_

CHRSTR

DMA Channel Reset

Request Register

F000 3C10

H

U, SV SV 0000 0000

H

DMA_

TRSR

DMA Transaction

Request State Register

F000 3C14

H

U, SV BE 0000 0000

H

DMA_

STREQ

DMA Software

Transaction Request

Register

F000 3C18

H

U, SV SV 0000 0000

H

DMA_

HTREQ

DMA Hardware

Transaction Request

Register

F000 3C1C

H

U, SV SV 0000 0000

H

DMA_

EER

DMA Enable Error

Register

F000 3C20

H

U, SV SV 0000 0000

H

DMA_

ERRSR

DMA Error Status

Register

F000 3C24

H

U, SV BE 0000 0000

H

DMA_

CLRE

DMA Clear Error

Register

F000 3C28

H

U, SV SV 0000 0000

H

DMA_

GINTR

DMA Global Interrupt Set

Register

F000 3C2C

H

U, SV SV 0000 0000

H

DMA_

MESR

DMA Move Engine

Status Register

F000 3C30

H

U, SV BE 0000 0000

H

DMA_

ME0R

DMA Move Engine 0

Read Register

F000 3C34

H

U, SV BE 0000 0000

H

DMA_

ME1R

DMA Move Engine 1

Read Register

F000 3C38

H

U, SV BE 0000 0000

H

DMA_

ME0PR

DMA Move Engine 0

Pattern Register

F000 3C3C

H

U, SV SV 0000 0000

H

Loading...

Loading...