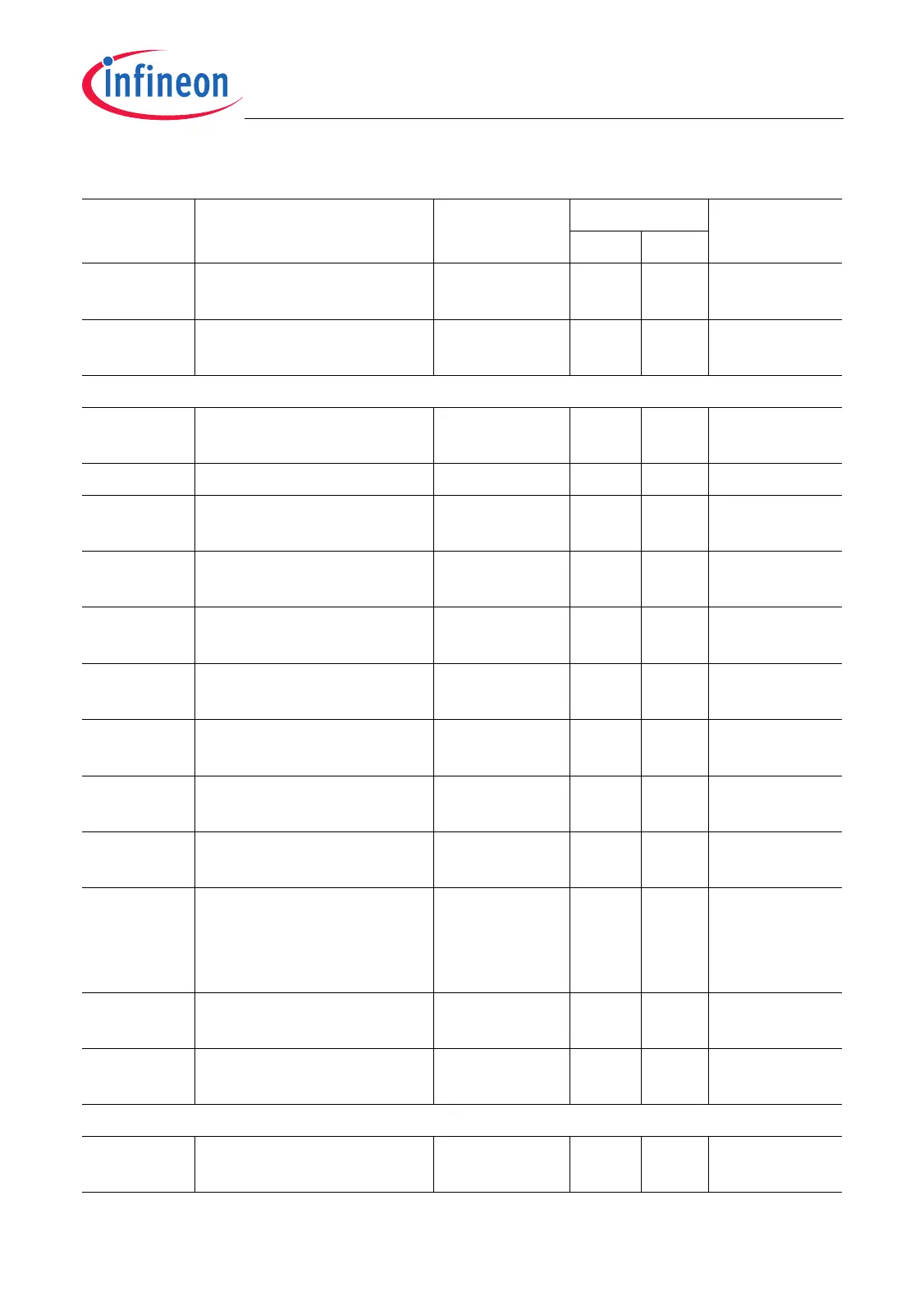

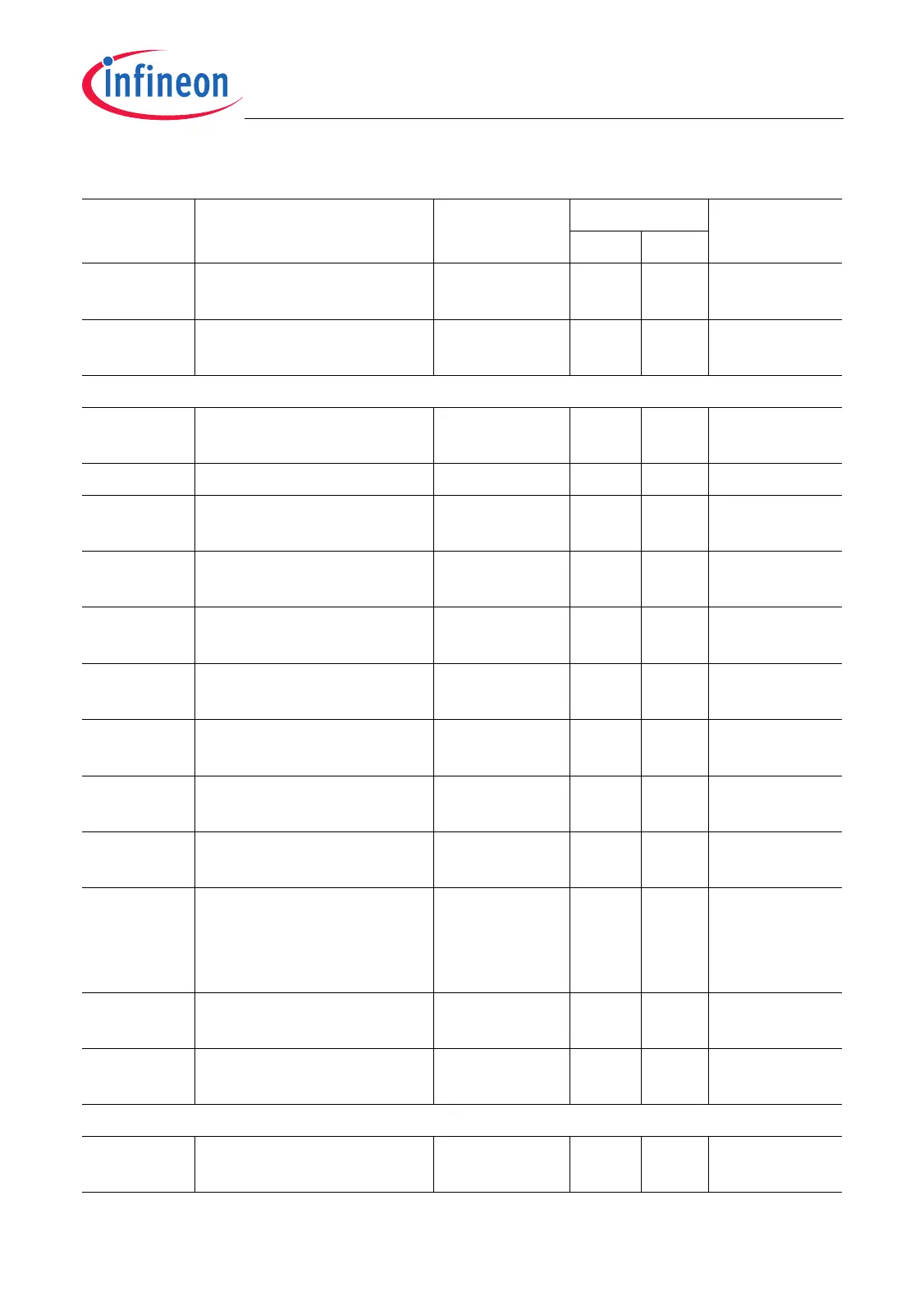

TC1796

System Units (Vol. 1 of 2)

Register Overview

User’s Manual 18-108 V2.0, 2007-07

Regs, V2.0

CPM1 Code Protection Mode

Register Set 1

F7E1 E280

H

U, SV,

32

SV,

32

0000 0000

H

– Reserved F7E1 E284

H

-

F7E1 EFFC

H

nE nE –

Core Debug Register (OCDS)

DBGSR Debug Status Register F7E1 FD00

H

U, SV,

32

SV,

32

0000 0000

H

– Reserved F7E1 FD04

H

nE nE –

EXEVT External Break Input

Event Specifier Register

F7E1 FD08

H

U, SV,

32

SV,

32

0000 0000

H

CREVT Core SFR Access Break

Event Specifier Register

F7E1FD0C

H

U, SV,

32

SV,

32

0000 0000

H

SWEVT Software Break Event

Specifier Register

F7E1 FD10

H

U, SV,

32

SV,

32

0000 0000

H

– Reserved F7E1 FD14

H

-

F7E1 FD1C

H

nE nE –

TR0EVT Trigger Event 0 Specifier

Register

F7E1 FD20

H

U, SV,

32

SV,

32

0000 0000

H

TR1EVT Trigger Event 1 Specifier

Register

F7E1 FD24

H

U, SV,

32

SV,

32

0000 0000

H

– Reserved F7E1 FD28

H

-

F7E1 FD3C

H

nE nE –

DMS Debug Monitor Start

Address Register

F7E1 FD40

H

U, SV,

32

U,

SV,

32,

NC

DE00 0000

H

DCX Debug Context Save Area

Pointer

F7E1 FD44

H

U, SV,

32

SV,

32

DE80 0000

H

– Reserved F7E1 FD48

H

-

F7E1 FDFC

H

nE nE –

Core Special Function Registers (CSFR)

PCXI Previous Context

Information Register

F7E1 FE00

H

U, SV,

32

SV,

32

0000 0000

H

Table 18-33 Address Map of CPU Core SFRs & GPRs (cont’d)

Short

Name

Description Address Access Mode Reset Value

Read Write

Loading...

Loading...