TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-21 V2.0, 2007-07

CPU, V2.0

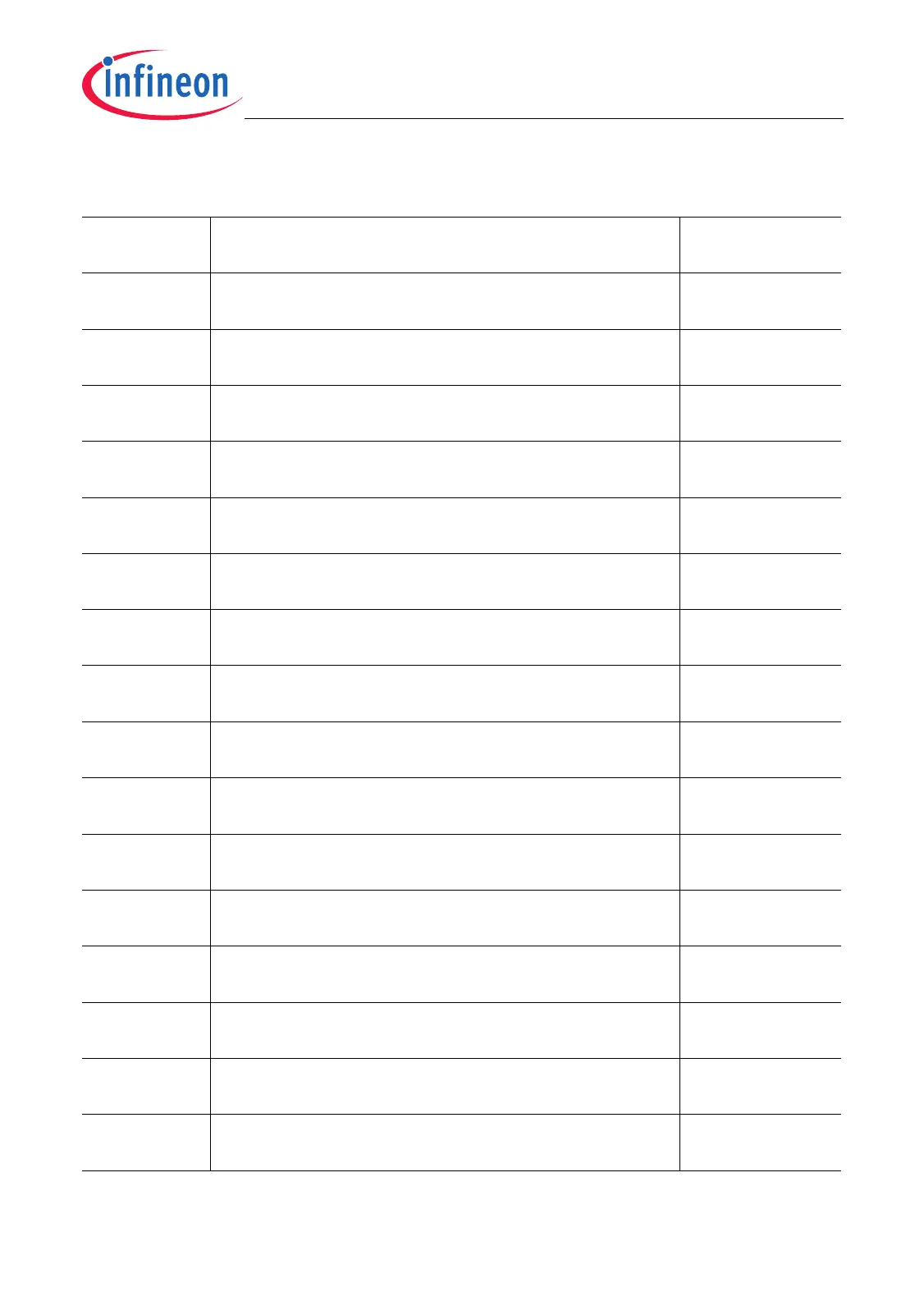

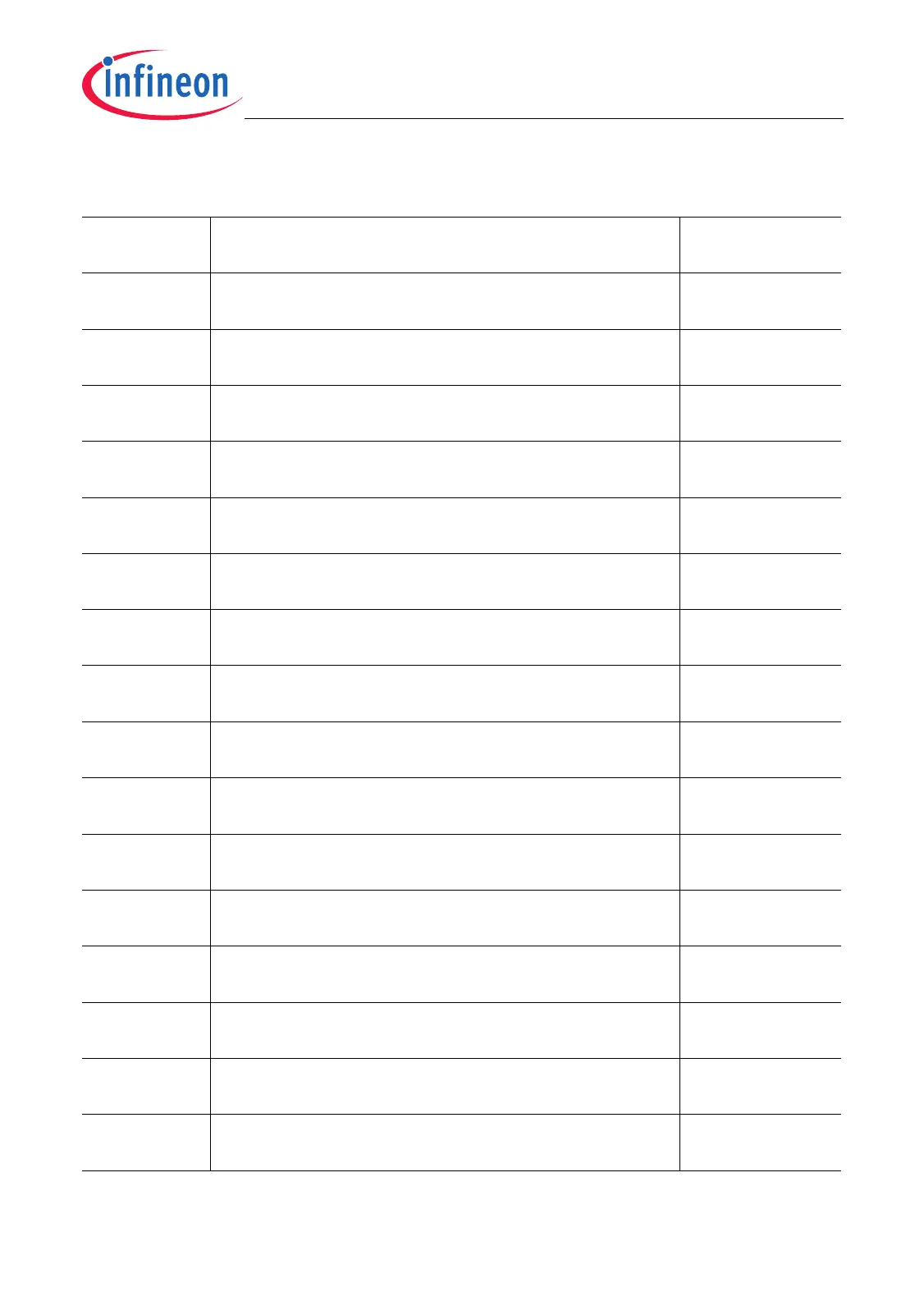

Table 2-6 Memory Protection Registers

Register

Short Name

Register Long Name Address

DPR0_0L Data Segment Protection Register Set 0, Range 0,

Lower Boundary

F7E1 C000

H

DPR0_0U Data Segment Protection Register Set 0, Range 0,

Upper Boundary

F7E1 C004

H

DPR0_1L Data Segment Protection Register Set 0, Range 1,

Lower Boundary

F7E1 C008

H

DPR0_1U Data Segment Protection Register Set 0, Range 1,

Upper Boundary

F7E1 C00C

H

DPR0_2L Data Segment Protection Register Set 0, Range 2,

Lower Boundary

F7E1 C010

H

DPR0_2U Data Segment Protection Register Set 0, Range 2,

Upper Boundary

F7E1 C014

H

DPR0_3L Data Segment Protection Register Set 0, Range 3,

Lower Boundary

F7E1 C018

H

DPR0_3U Data Segment Protection Register Set 0, Range 3,

Upper Boundary

F7E1 C01C

H

DPR1_0L Data Segment Protection Register Set 1, Range 0,

Lower Boundary

F7E1 C400

H

DPR1_0U Data Segment Protection Register Set 1, Range 0,

Upper Boundary

F7E1 C404

H

DPR1_1L Data Segment Protection Register Set 1, Range 1,

Lower Boundary

F7E1 C408

H

DPR1_1U Data Segment Protection Register Set 1, Range 1,

Upper Boundary

F7E1 C40C

H

DPR1_2L Data Segment Protection Register Set 1, Range 2,

Lower Boundary

F7E1 C410

H

DPR1_2U Data Segment Protection Register Set 1, Range 2,

Upper Boundary

F7E1 C414

H

DPR1_3L Data Segment Protection Register Set 1, Range 3,

Lower Boundary

F7E1 C418

H

DPR1_3U Data Segment Protection Register Set 1, Range 3,

Upper Boundary

F7E1 C41C

H

Loading...

Loading...