TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-35 V2.0, 2007-07

SSC, V2.1

The Error Flag Modification Register EFM is required for clearing or setting the four error

flags which are located in register STAT.

0 [7:4],

[31:13]

r Reserved

Read as 0; should be written with 0.

EFM

Error Flag Modification Register (2C

H

) Reset Value: 0000 0000

H

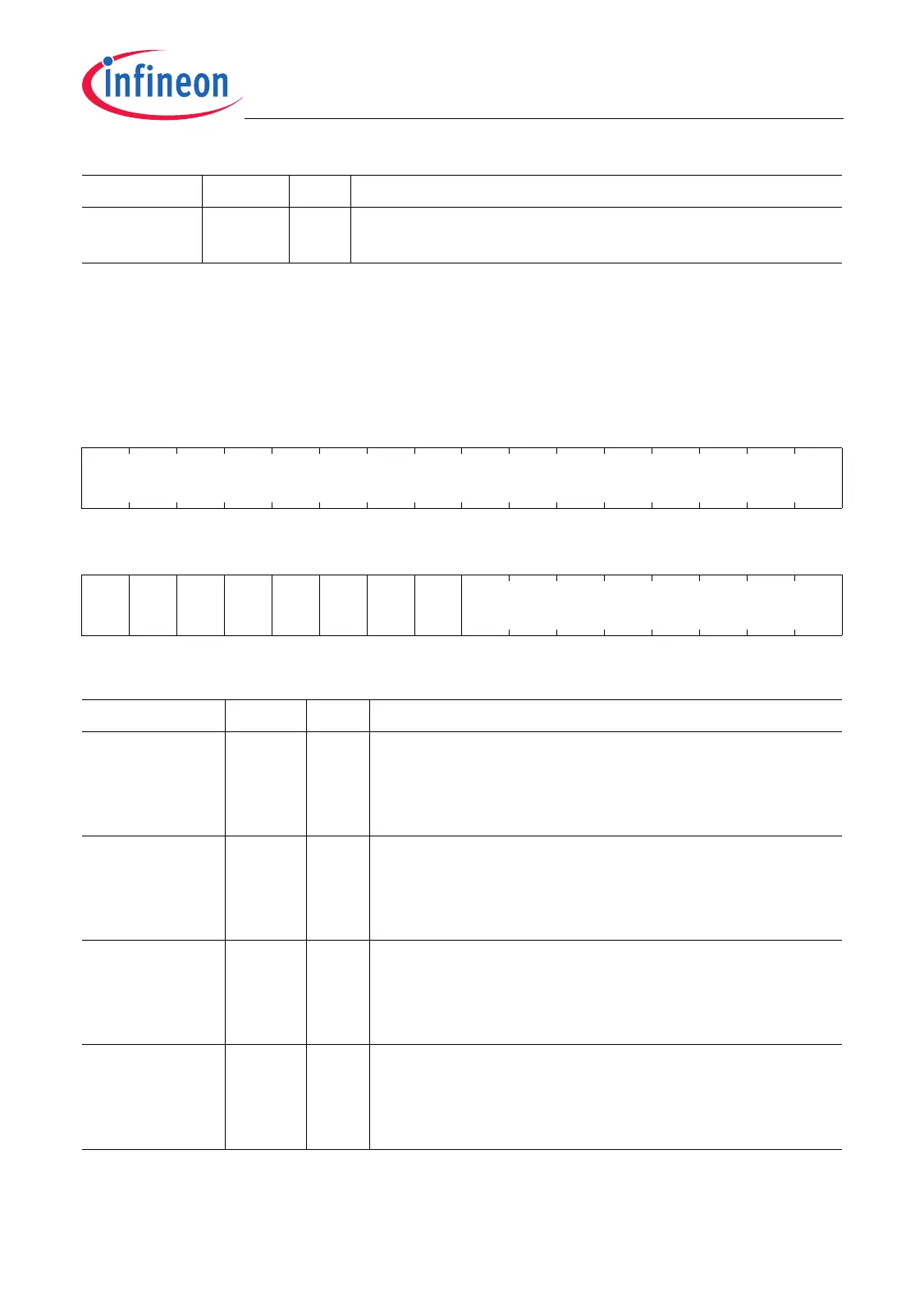

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

SET

BE

SET

PE

SET

RE

SET

TE

CLR

BE

CLR

PE

CLR

RE

CLR

TE

0

wwwwwwww r

Field Bits Type Description

CLRTE 8wClear Transmit Error Flag

0

B

No effect.

1

B

Bit STAT.TE is cleared.

Bit is always read as 0.

CLRRE 9wClear Receive Error Flag

0

B

No effect.

1

B

Bit STAT.RE is cleared.

Bit is always read as 0.

CLRPE 10 w Clear Phase Error Flag

0

B

No effect.

1

B

Bit STAT.PE is cleared.

Bit is always read as 0.

CLRBE 11 w Clear Baud Rate Error Flag

0

B

No effect.

1

B

Bit STAT.BE is cleared.

Bit is always read as 0.

Field Bits Type Description

Loading...

Loading...