TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-36 V2.0, 2007-07

SSC, V2.1

Note: When the set and clear bits for an error flag are set at the same time during an

EFM write operation (e.g SETPE = CLRPE = 1), the error flag in STAT is not

affected.

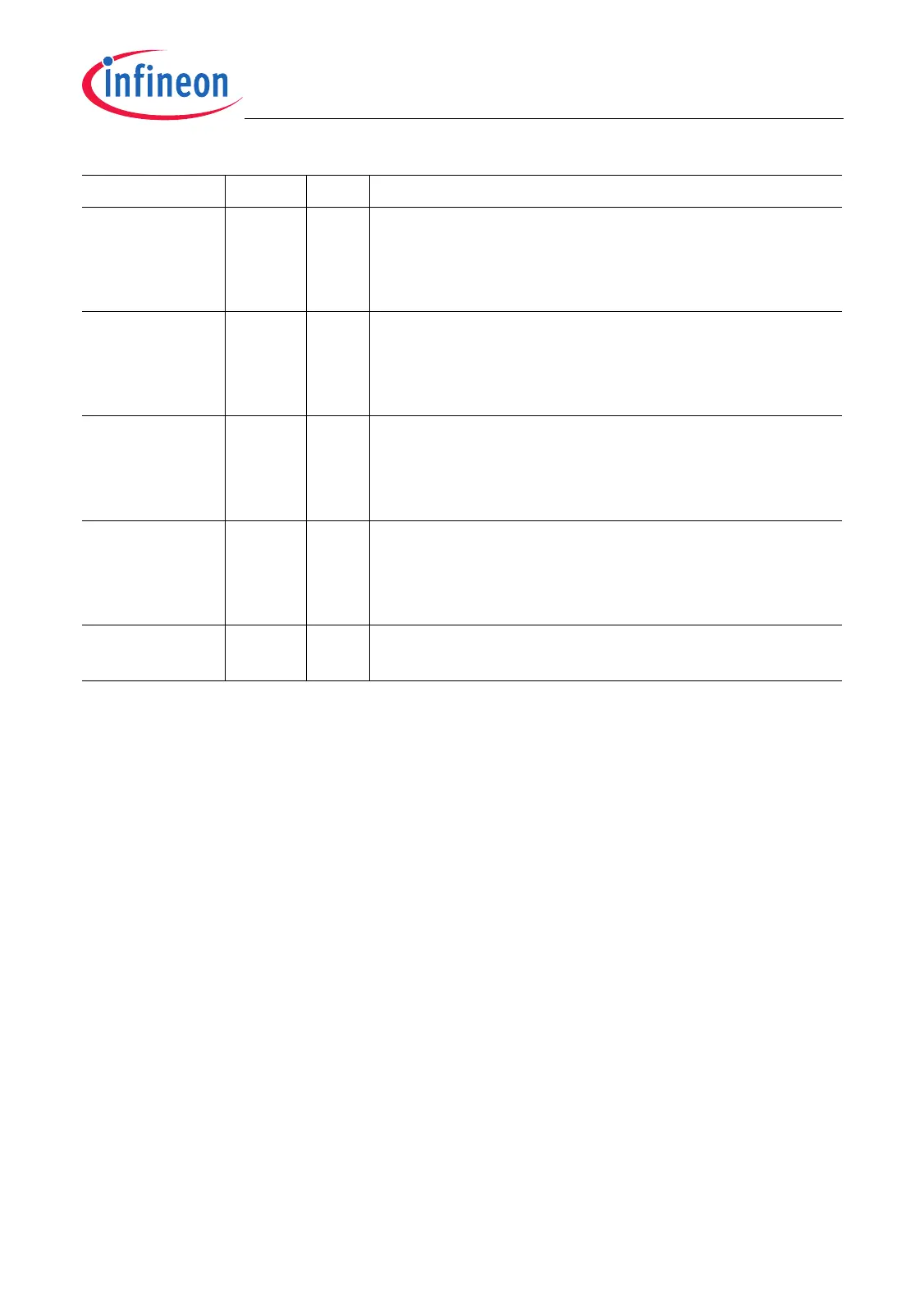

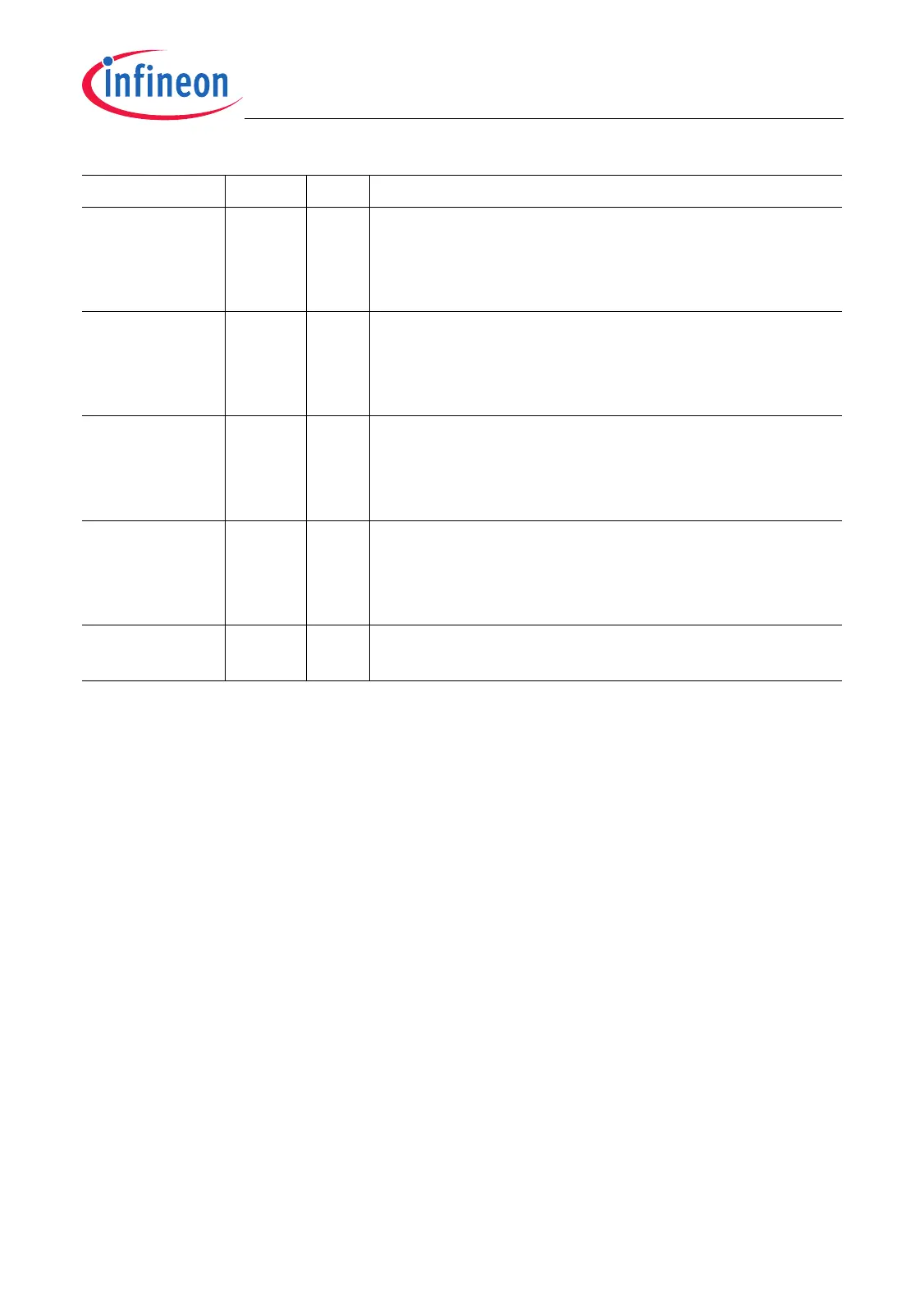

SETTE 12 w Set Transmit Error Flag

0

B

No effect.

1

B

Bit STAT.TE is set.

Bit is always read as 0.

SETRE 13 w Set Receive Error Flag

0

B

No effect.

1

B

Bit STAT.RE is set.

Bit is always read as 0.

SETPE 14 w Set Phase Error Flag

0

B

No effect.

1

B

Bit STAT.PE is set.

Bit is always read as 0.

SETBE 15 w Set Baud Rate Error Flag

0

B

No effect.

1

B

Bit STAT.BE is set.

Bit is always read as 0.

0 [7:0],

[31:16]

r Reserved

Read as 0; should be written with 0.

Field Bits Type Description

Loading...

Loading...