TC1796

Peripheral Units (Vol. 2 of 2)

Synchronous Serial Interface (SSC)

User’s Manual 20-44 V2.0, 2007-07

SSC, V2.1

The FIFO Status Register FSTAT (only available in SSC0) indicates the filling levels of

the Receive and Transmit FIFOs.

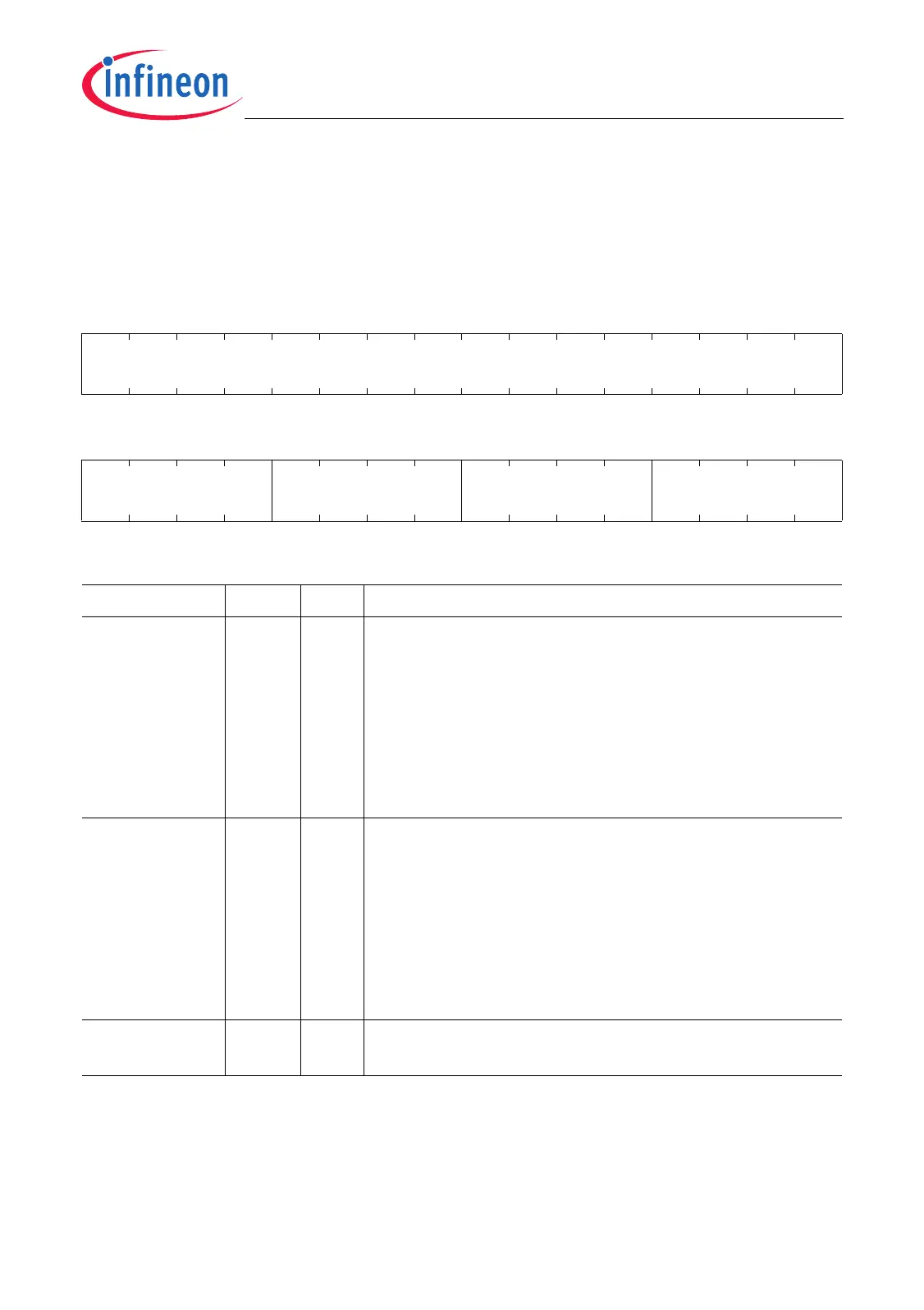

SSC0_FSTAT

SSC0 FIFO Status Register (38

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0 TXFFL 0 RXFFL

rrhrrh

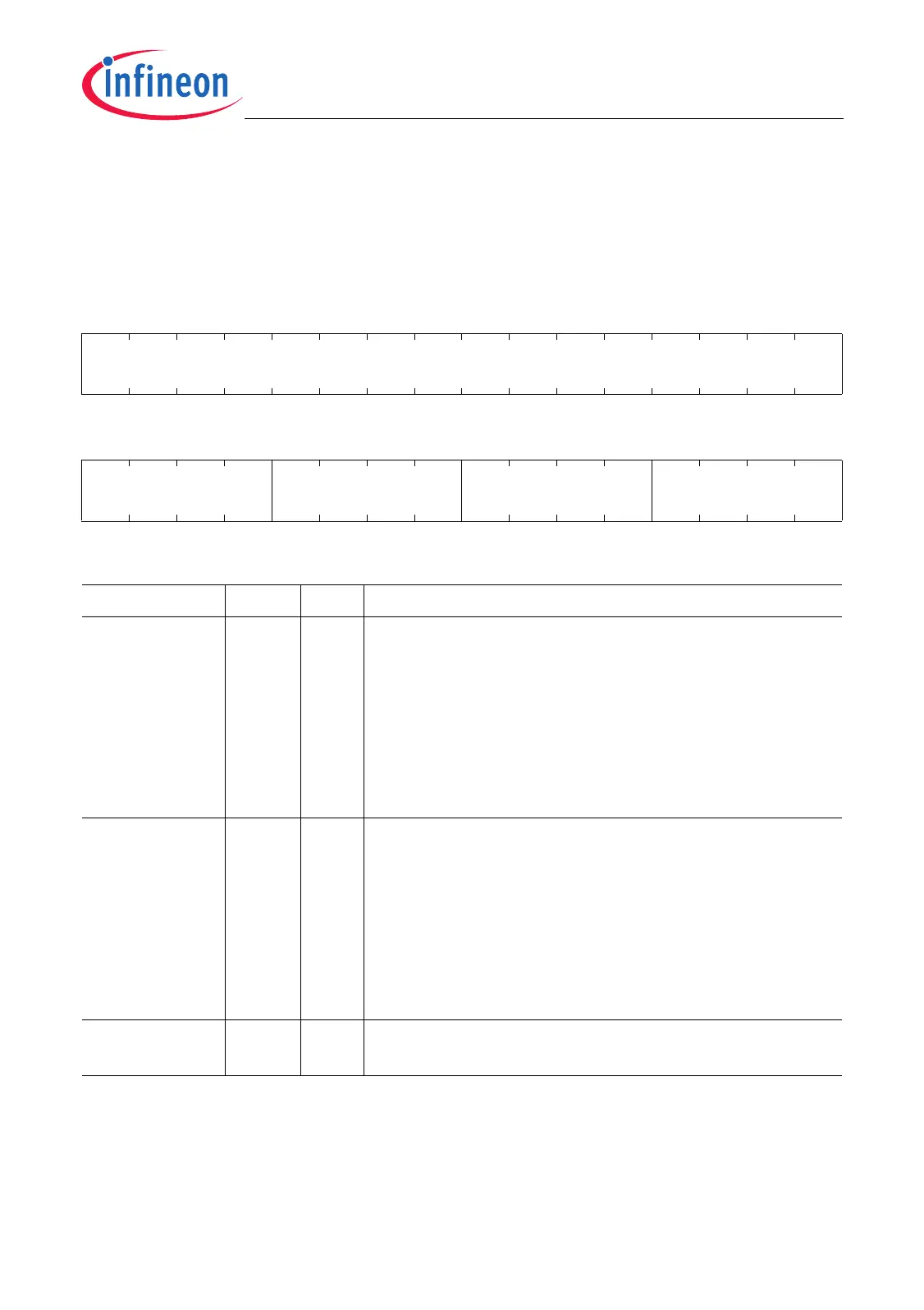

Field Bits Type Description

RXFFL [3:0] rh RXFIFO Filling Level

1)2)

This bit field indicates the filling level of the RXFIFO.

0000

B

RXFIFO is filled with 0 bytes

0001

B

RXFIFO is filled with 1 byte

…

B

…

0111

B

RXFIFO is filled with 7 bytes

1000

B

RXFIFO is filled with 8 bytes

RXFFL is cleared after a RXFIFO flush operation.

1) The data width of a RXFIFO and TXFIFO stage can be programmed from 2 to 15 bits. The data width “byte”

mentioned in this description represents a data width of 8 bits.

2) In the SSC0 module with 8-stage RXFIFO and TXFIFO, the most significant bits of RXFFL and TXFFL

(FSTAT.4 and FSTAT.12) are always read as 0 and should be written with 0.

TXFFL [11:8] rh TXFIFO Filling Level

1)2)

This bit field indicates the filling level of the TXFIFO.

0000

B

TXFIFO is filled with 0 bytes

0001

B

TXFIFO is filled with 1 byte

…

B

…

0111

B

TXFIFO is filled with 7 bytes10

1000

B

TXFIFO is filled with 8 bytes

TXFFL is cleared after a TXFIFO flush operation.

0 [7:4],

[31:12]

r Reserved

Read as 0; should be written with 0.

Loading...

Loading...