TC1796

Peripheral Units (Vol. 2 of 2)

Micro Second Channel (MSC)

User’s Manual 21-29 V2.0, 2007-07

MSC, V2.0

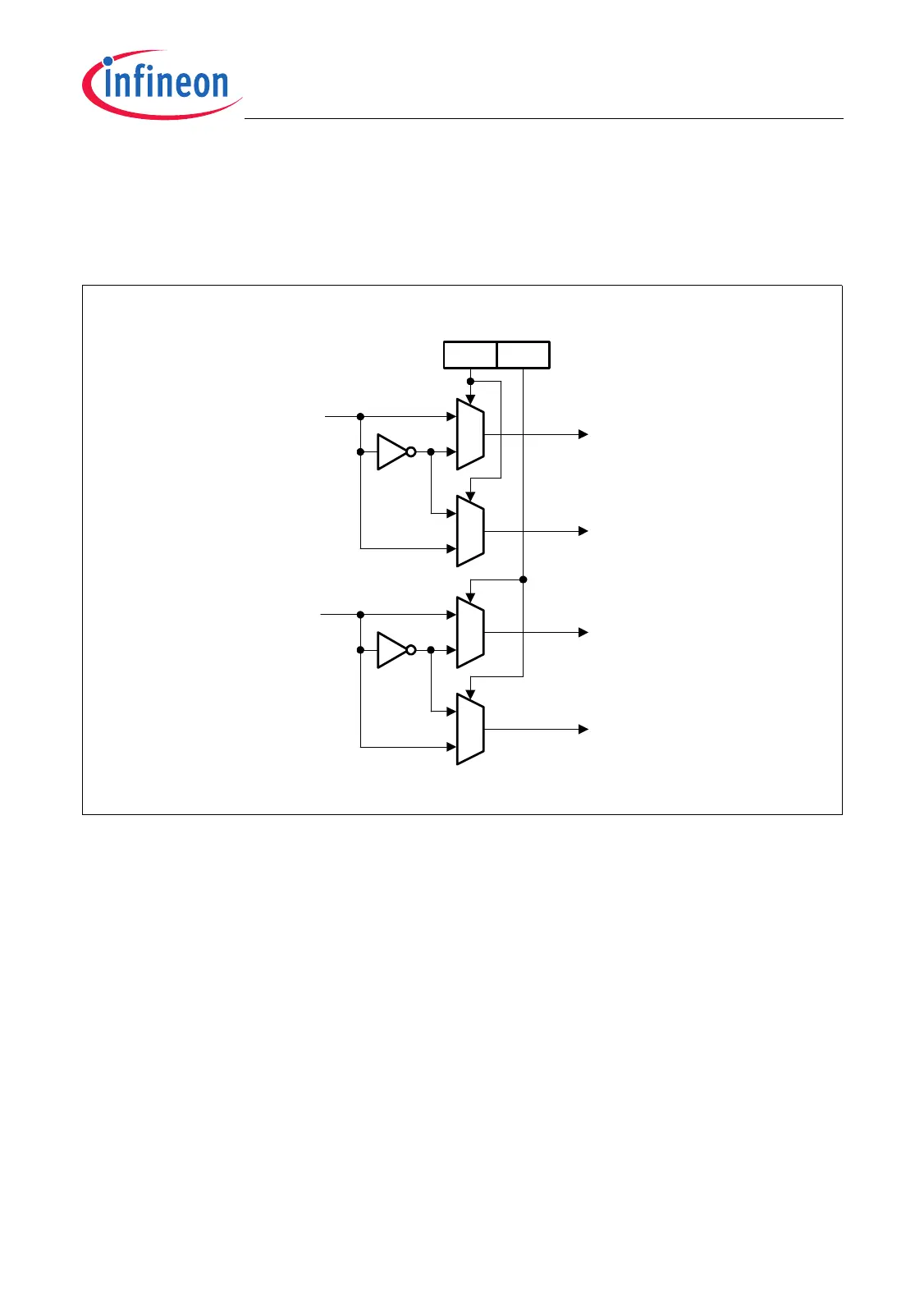

At the MSC downstream channel, the internal serial clock output FCL and data output

line SO are available outside the MSC module as two signal pairs with inverted signal

polarity, FCLP/FCLN and SOP/SON. Both, clock and data outputs, are generated from

the module internal signals FCL and SO according to Figure 21-21.

Figure 21-21 Downstream Channel: Clock and Data Output Control

With OCR.CLP = 0, FCLP has identical and FCLN has inverted polarity compared to

FCL. Setting OCR.CLP, exchanges the signal polarities of FCLP and FCLN. An

equivalent control capability is available for the SOP and SON data outputs (controlled

by OCR.SLP).

One additional control capability not shown in Figure 21-21 is available for the FCL

signal. With OCR.CLKCTRL = 1, the FCL clock signal will always be generated,

independently whether a downstream frame is currently transmitted or not. If

OCR.CLKCTRL = 0, FCL becomes only active during the active phases of data or

command frames (not during passive time frames).

MCA05815

1

0

CLP

OCR

FCLP

FCLN

SOP

SON

SLP

FCL

SO

1

0

1

0

1

0

Loading...

Loading...