TC1796

Peripheral Units (Vol. 2 of 2)

Micro Second Channel (MSC)

User’s Manual 21-52 V2.0, 2007-07

MSC, V2.0

The Interrupt Status Register ISR holds the interrupt status flags that indicate an

interrupt occurrence in downstream and upstream channels.

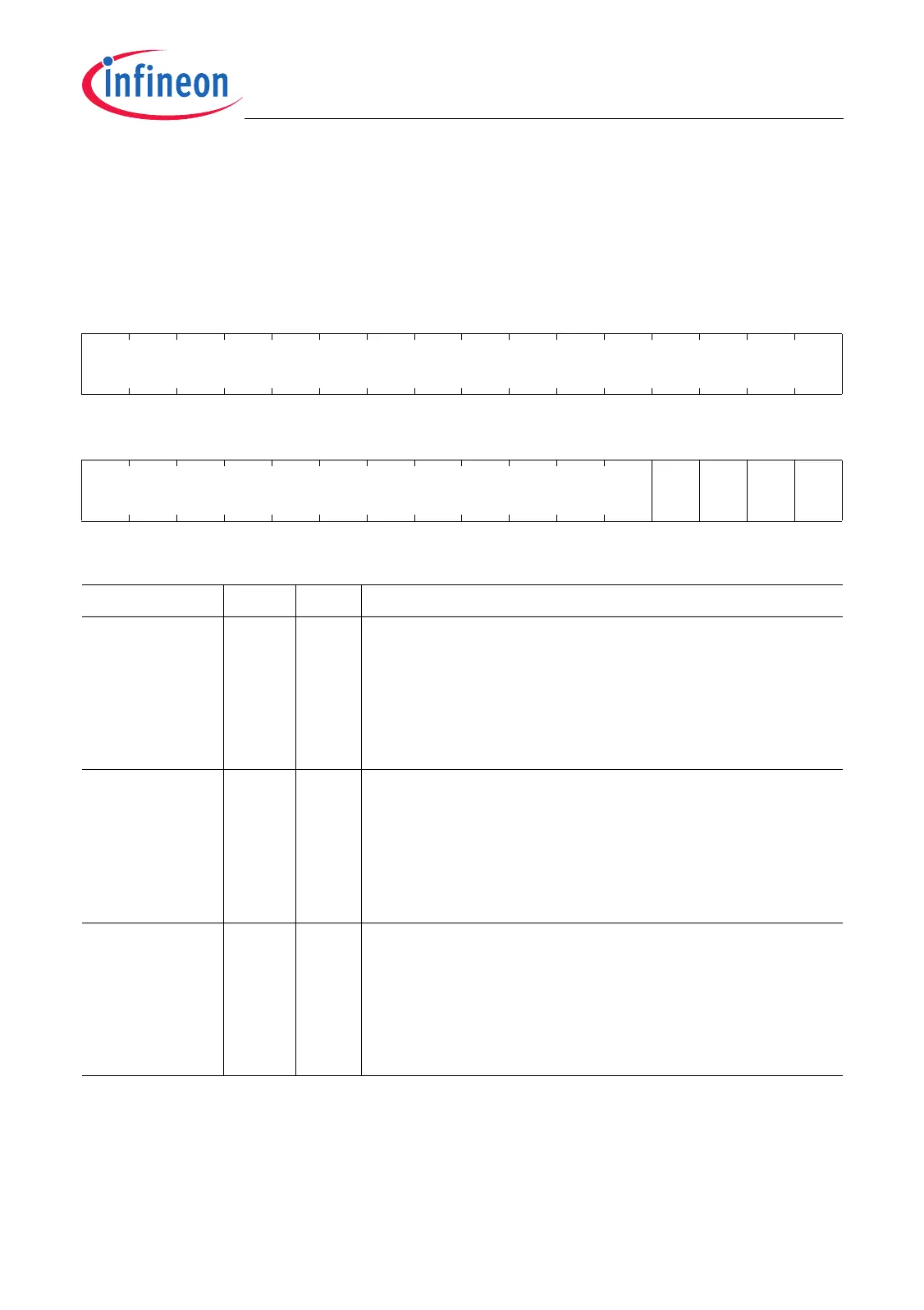

ISR

Interrupt Status Register (44

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

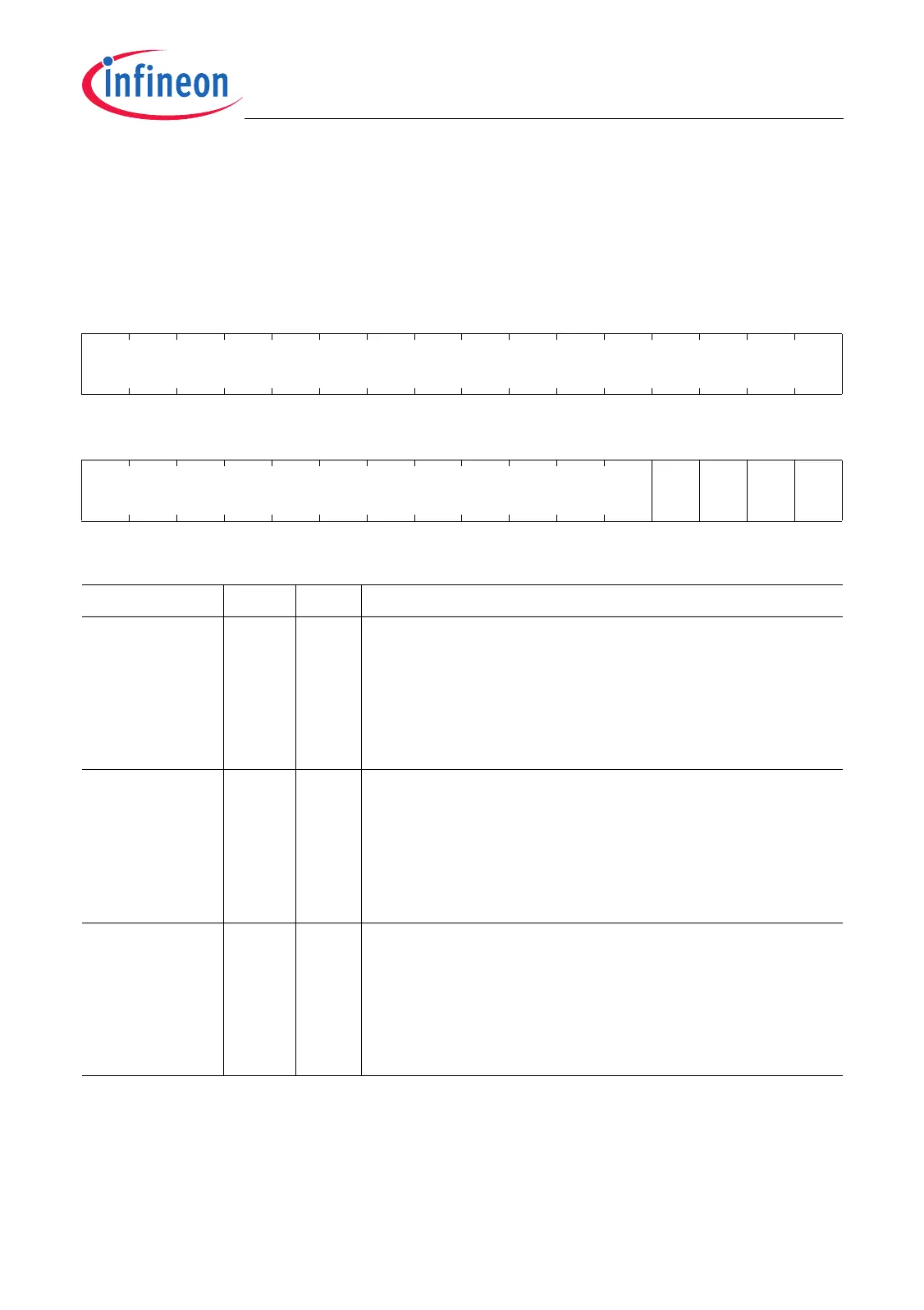

1514131211109876543210

0URDIDTFIDECIDEDI

r rhrhrhrh

Field Bits Type Description

DEDI 0rhData Frame Interrupt Flag

This flag is always set by hardware when a

downstream channel data frame interrupt is

generated. DEDI can be set or cleared by software

when writing to register ISC with the appropriate bits

ISC.SDEDI or ISC.CDEDI set.

DECI 1rhCommand Frame Interrupt Flag

This flag is always set by hardware when a

downstream channel command frame interrupt is

generated, whether or not it is enabled. DECI can be

set or cleared by software when writing to register ISC

with the appropriate bits SDECI or CDECI set.

DTFI 2rhTime Frame Interrupt Flag

This flag is always set by hardware when a

downstream channel time frame interrupt is

generated, whether or not it is enabled. DTFI can be

set or cleared by software when writing to register ISC

with the appropriate bits SDTFI or CDTFI set.

Loading...

Loading...