TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-39 V2.0, 2007-07

CPU, V2.0

The DMI Asynchronous Trap Flag Register, DMI_ATR, holds the flags that inform about

the root cause of a Data Access Asynchronous Bus Error (ASE). Reading DMI_ATR in

supervisor mode returns the register contents and then clears its contents. Reading

DMI_ATR in user mode returns the contents of the register but does not clear its

contents.

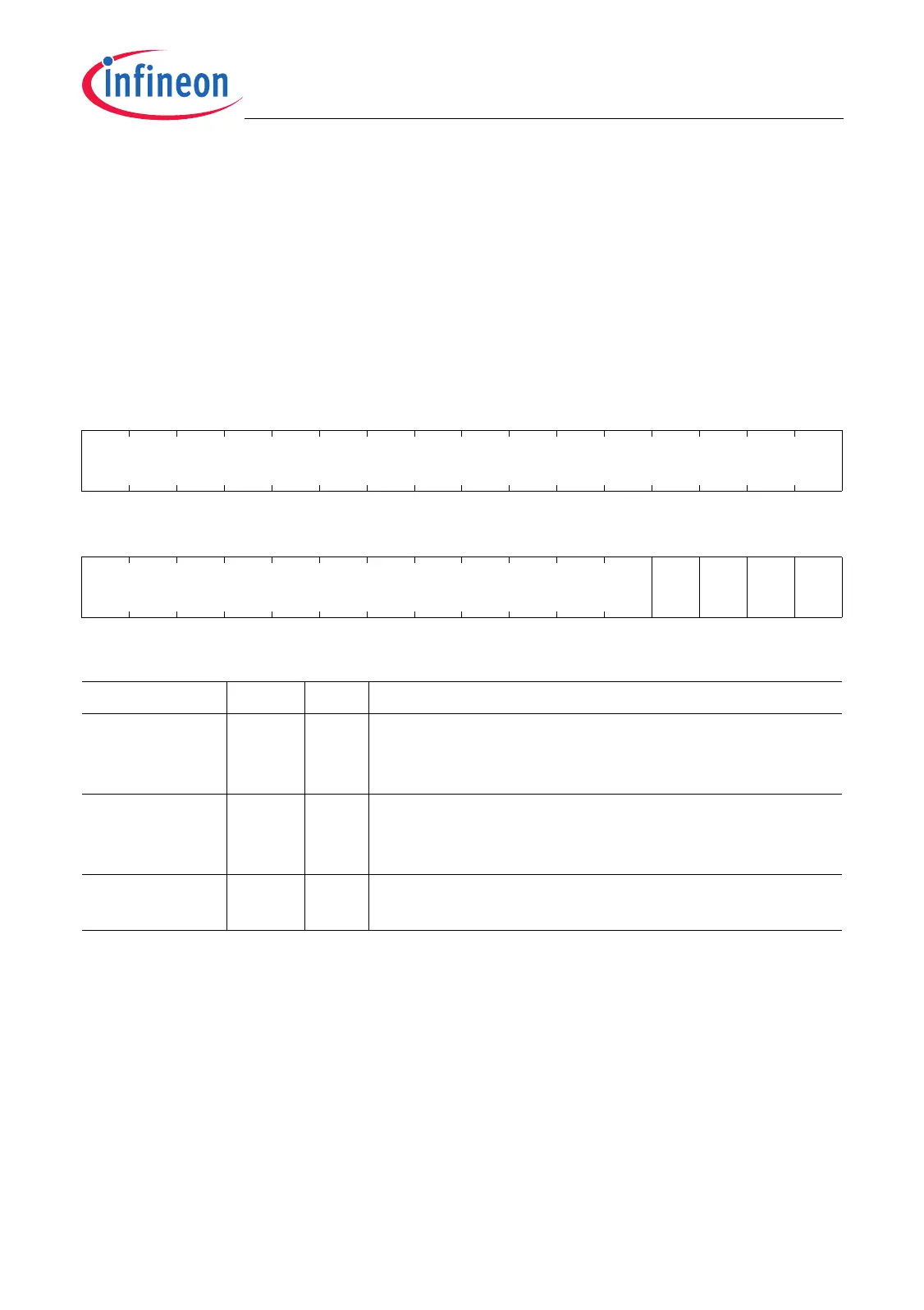

DMI_ATR

DMI Asynchronous Trap Flag Register

(F87FFC20

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

SBE

ATF

0

SRE

ATF

0

rrhrrhr

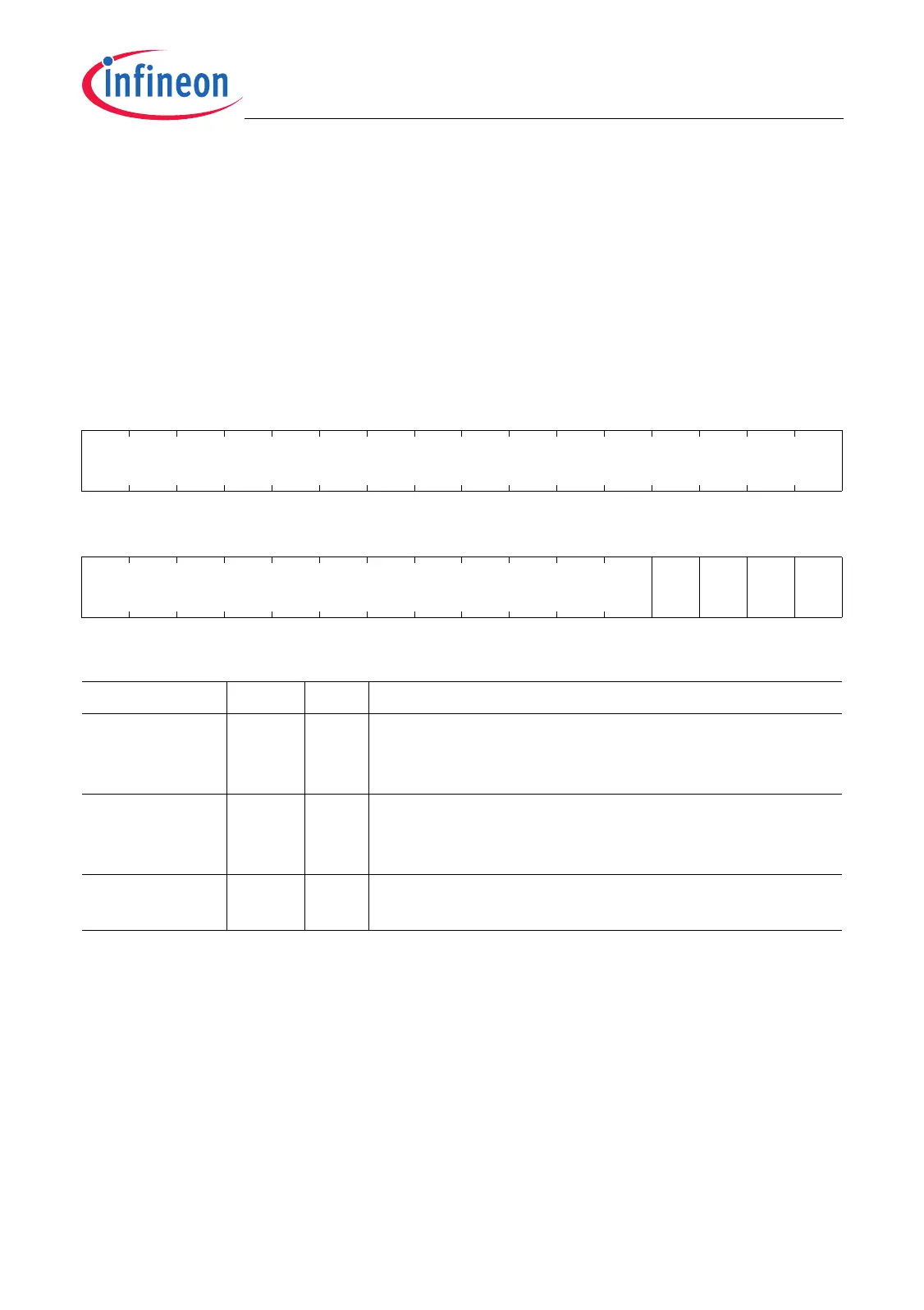

Field Bits Type Description

SREATF 1rhStore Range Asynchronous Error

0

B

No error

1

B

Store range asynchronous error has occurred

SBEATF 3rhLMB Bus Store Asynchronous Error

0

B

No error

1

B

Bus store asynchronous error has occurred

0 0, 2,

[31:4]

r Reserved

Returns 0 when read.

Loading...

Loading...