TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-67 V2.0, 2007-07

MultiCAN, V2.0

The Interrupt Trigger Register ITR is used to trigger interrupt requests on each interrupt

output line by software.

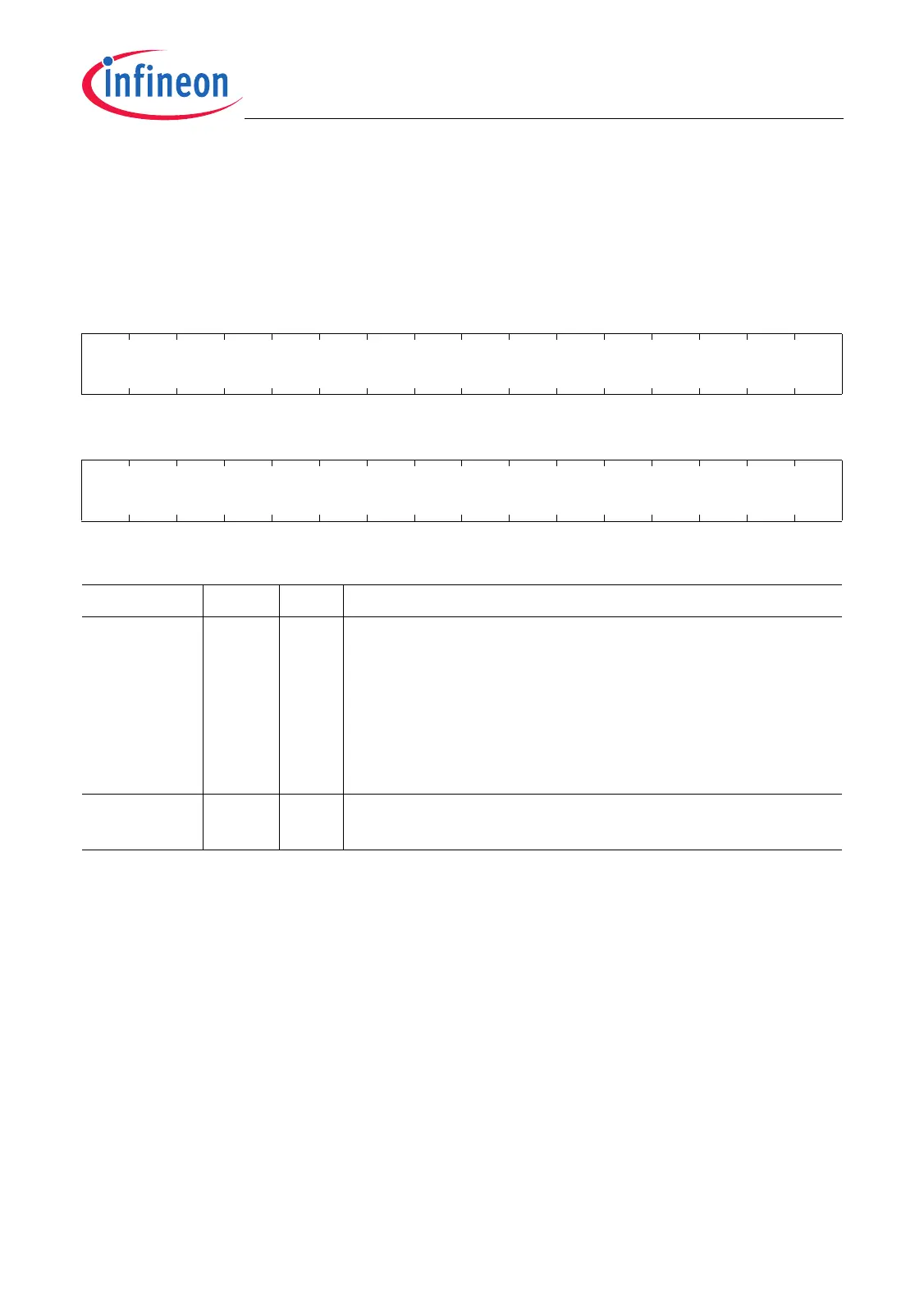

MITR

Module Interrupt Trigger Register (1CC

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

IT

w

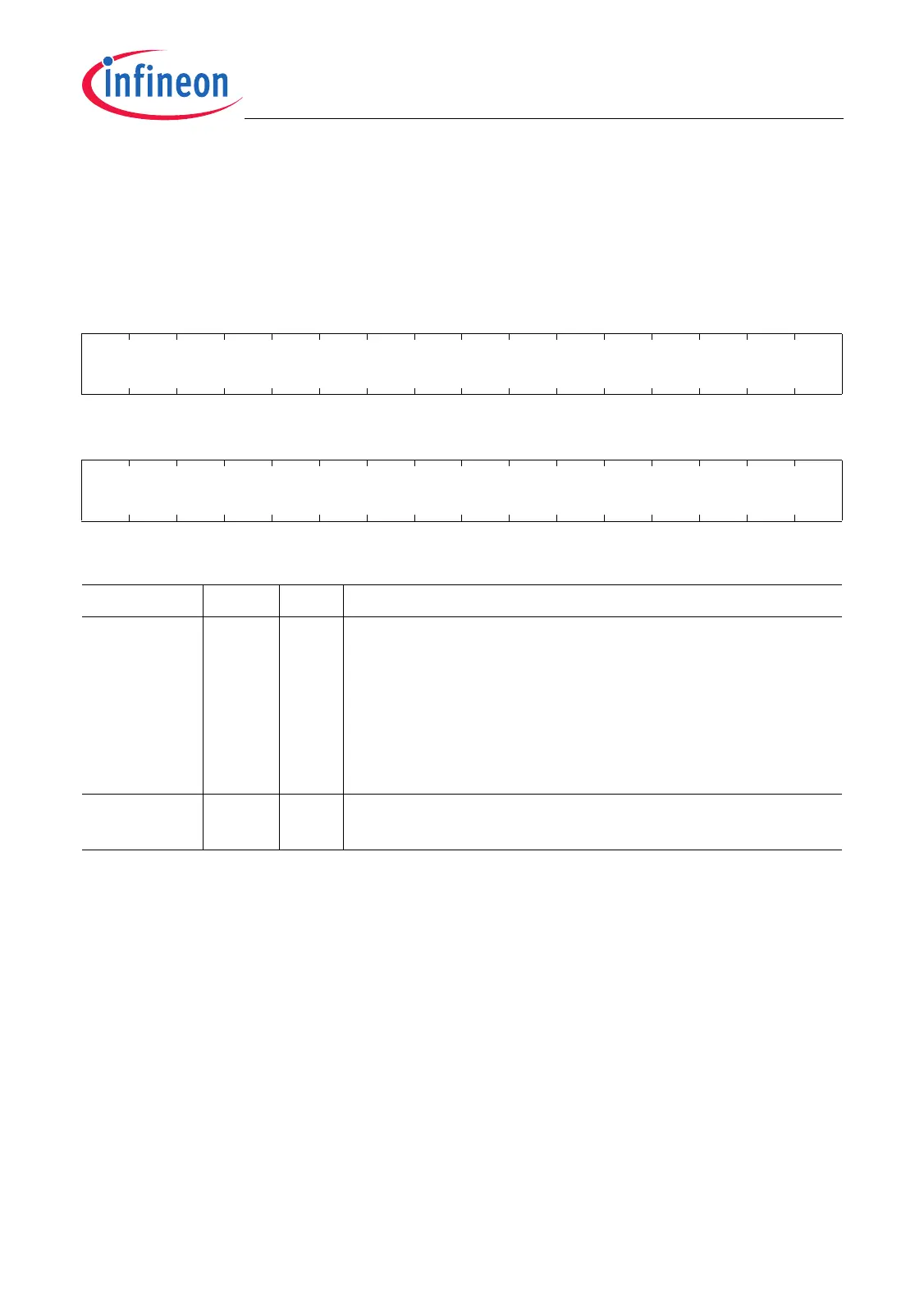

Field Bits Type Description

IT [15:0] w Interrupt Trigger

Writing a 1 to IT[n] (n = 0-15) generates an interrupt

request on interrupt output line INT_O[n]. Writing a 0 to

IT[n] has no effect. Bit field IT is always read as 0.

Multiple interrupt requests can be generated with a

single write operation to MITR by writing a 1 to several

bit positions of IT.

0 [31:16] r Reserved

Read as 0; should be written with 0.

Loading...

Loading...