TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-186 V2.0, 2007-07

MultiCAN, V2.0

TTIER

Time Trigger Interrupt Enable Register

(2D4

H

) Reset Value: 0000 0000

H

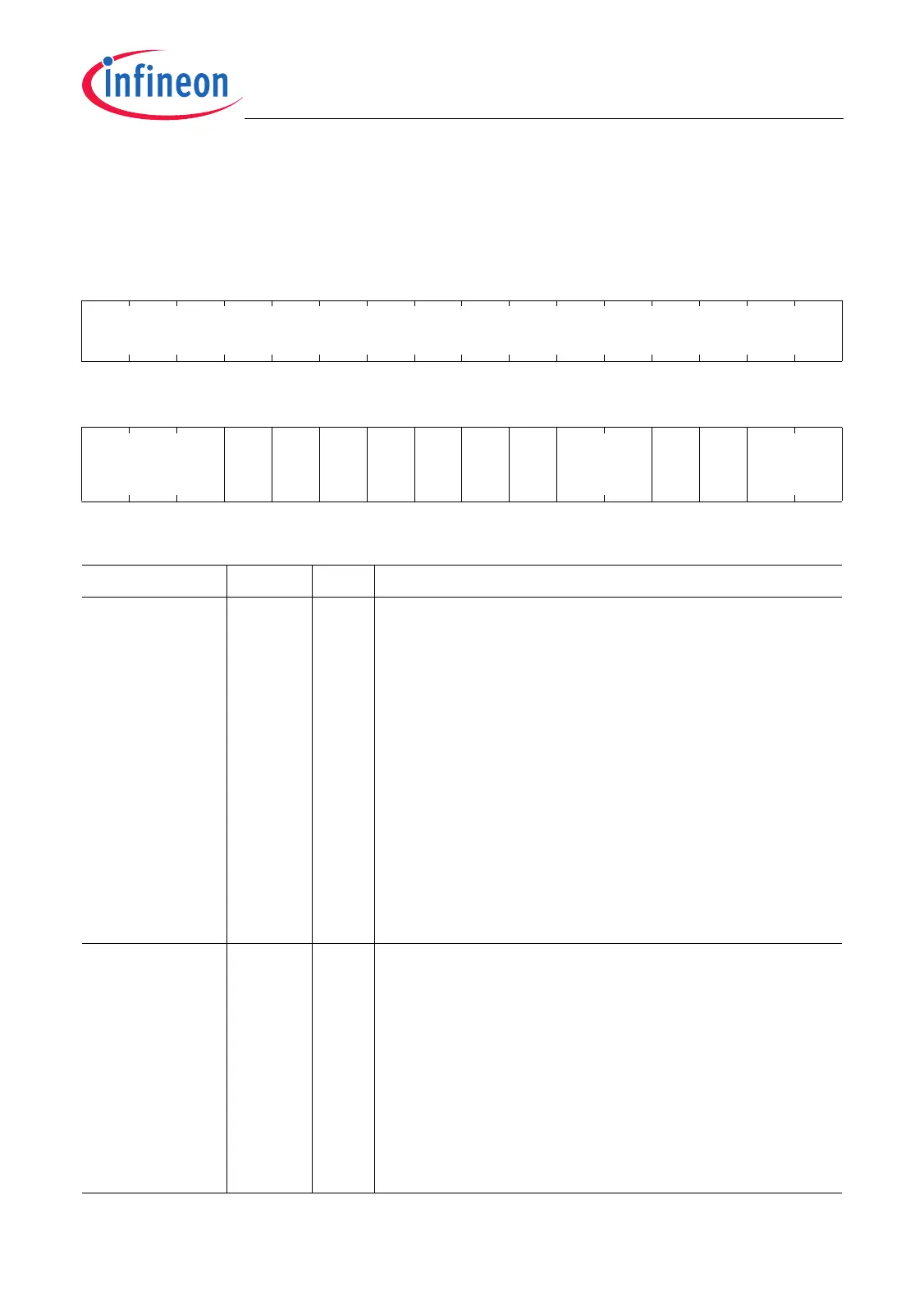

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

NOT

IF

IE

SE

IE

SYN

CSC

IE

MSR

C

IE

ERR

SC

IE

AWD

IE

WTE

IE

0

TT

ER

IE

TEN

WER

IE

NBC

IE

r rwrwrwrwrwrwrw r rwrw rw

Field Bits Type Description

NBCIE [1:0] rw New Basic Cycle Interrupt Enable

NBCIE enables the new basic or matrix cycle

interrupt. This interrupt is generated when either bit

TTIRR.NBC or bit TTIRR.NMC become set

(independent of its current state).

00

B

A new basic or matrix cycle interrupt is

disabled.

01

B

A basic cycle interrupt is generated whenever

TTIRR.NBC becomes set.

10

B

A matrix cycle interrupt is generated whenever

TTIRR.NMC becomes set.

11

B

Reserved

Bit field TTINPR.NBCINP selects the interrupt output

line that becomes activated at this type of interrupt.

TENWERIE 2rwTransmit Enable Window Error Interrupt Enable

TENWERIE enables the transmit enable window

error interrupt. This interrupt is generated when bit

TTIRR.TENWER is set.

0

B

Transmit enable window error interrupt is

disabled.

1

B

Transmit enable window error interrupt is

enabled.

Bit field TTINPR.ERRINP selects the interrupt output

line that becomes activated at this type of interrupt.

Loading...

Loading...