TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-193 V2.0, 2007-07

MultiCAN, V2.0

The TMV bit fields in the scheduler timing status registers monitor the time mark

information for the start of the next time window after the instruction collection phase of

the scheduler (collected from the TME, RME or BCE entries).

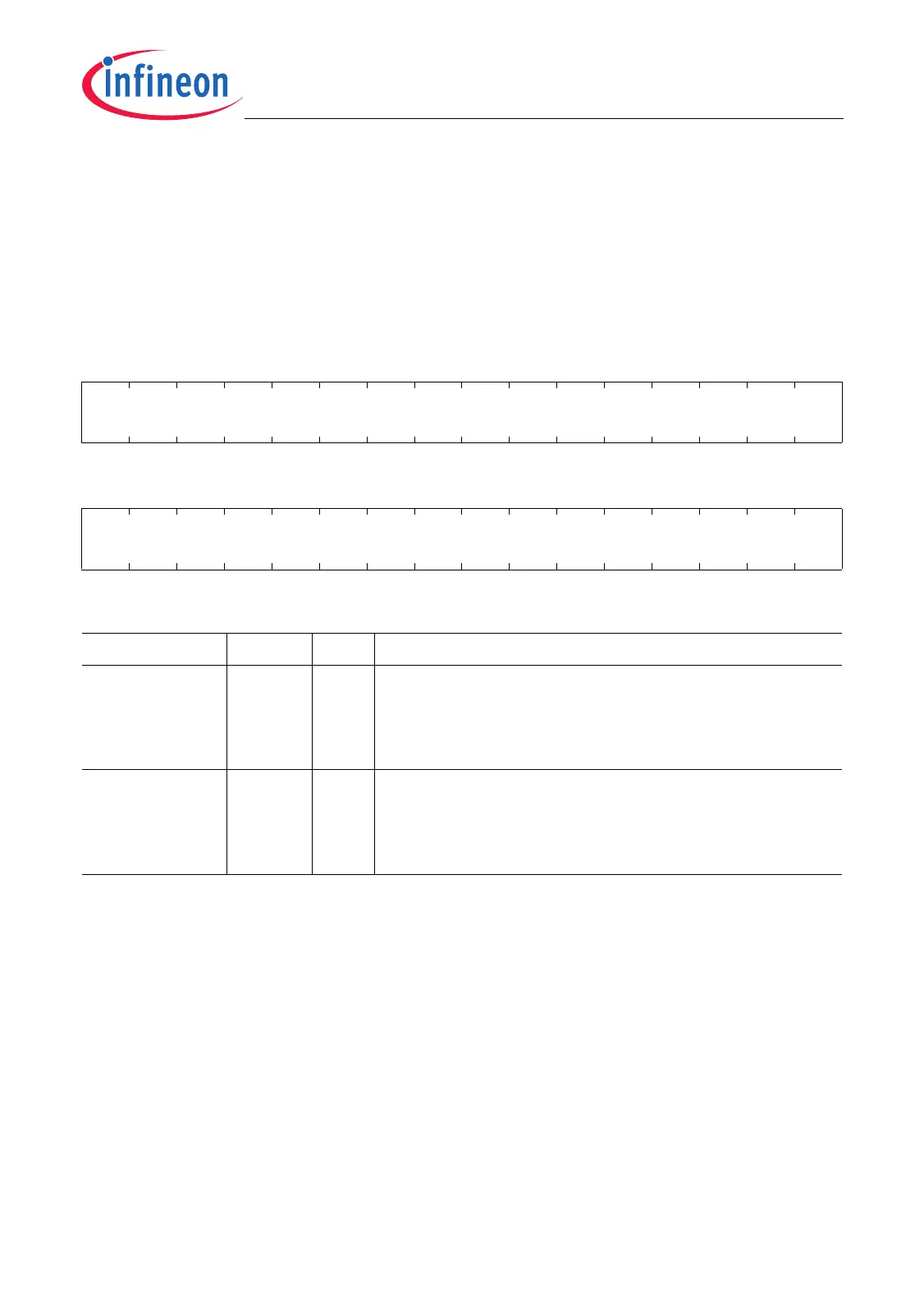

STSRL

Scheduler Timing Status Register Low

(2F0

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

BCETMV

rh

1514131211109876543210

RMETMV

rh

Field Bits Type Description

RMETMV [15:0] rh Time Mark Value from RME

This bit field indicates the compare value for the next

time mark defined by an RME. This value is valid

only if SISR.ICF = 1 and SISR.RMEV = 1.

BCETMV [31:16] rh Time Mark Value from BCE

This bit field indicates the compare value for the next

time mark defined by an BCE. This value is valid only

if SISR.ICF = 1.

Loading...

Loading...