TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-116 V2.0, 2007-07

MLI, V2.0

The Receiver Address Register RADRR is a read-only register storing the complete

address of the most recently (or currently) targeted Remote Window.

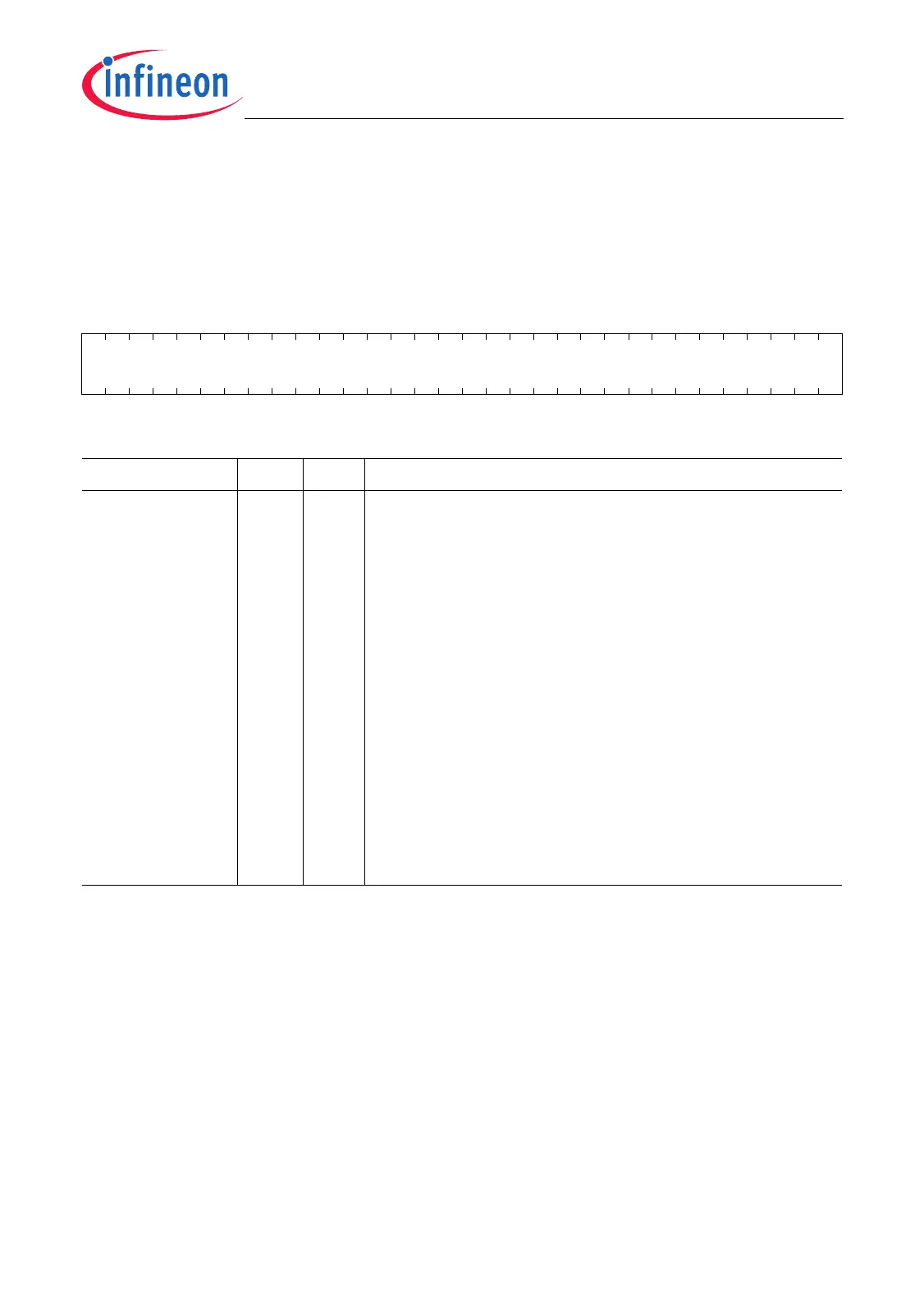

RADRR

Receiver Address Register (8C

H

) Reset Value: 0000 0000

H

31 0

ADDR

rh

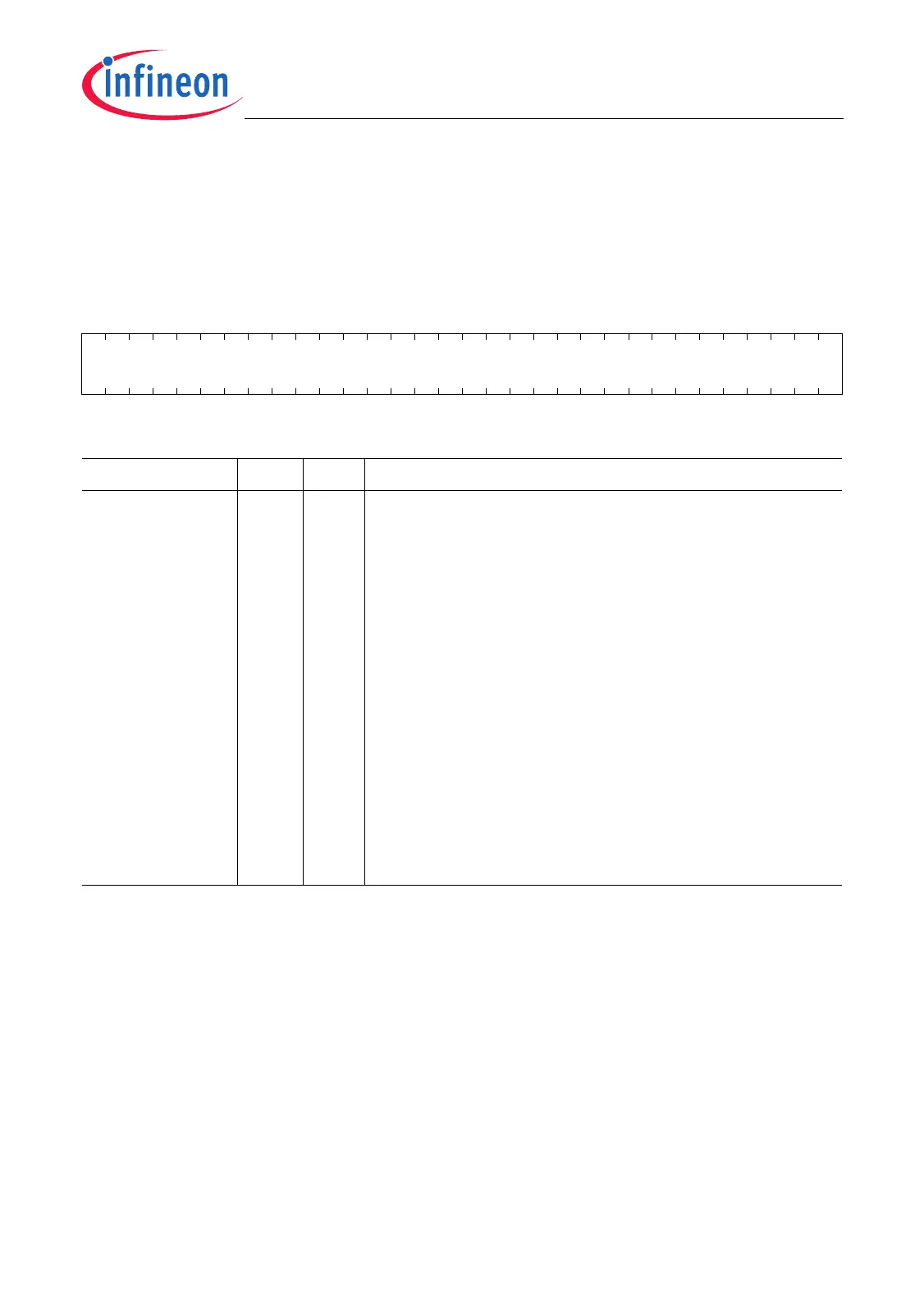

Field Bits Type Description

ADDR [31:0] rh Address

ADDR indicates the complete target address for the

most recently (or currently) targeted Remote Window

(pipe x).

When a Copy Base Address Frame is received,

ADDR is unchanged.

When a write or Read Frame with m bits of address

offset is received, bits ADDR[31:m] replaced by the

bits RPxBAR.ADDR[31:m] and bitsADDR[m-1:0] are

replaced by the received offset.

When an optimized read or data frame is received, the

address prediction mechanism adds the predicted

address offset RPxSTATR.AP to RPxBAR.ADDR and

stores the result in ADDR.

When an Answer Frame is received, ADDR becomes

invalid.

Loading...

Loading...