TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-181 V2.0, 2007-07

GPTA, V2.0

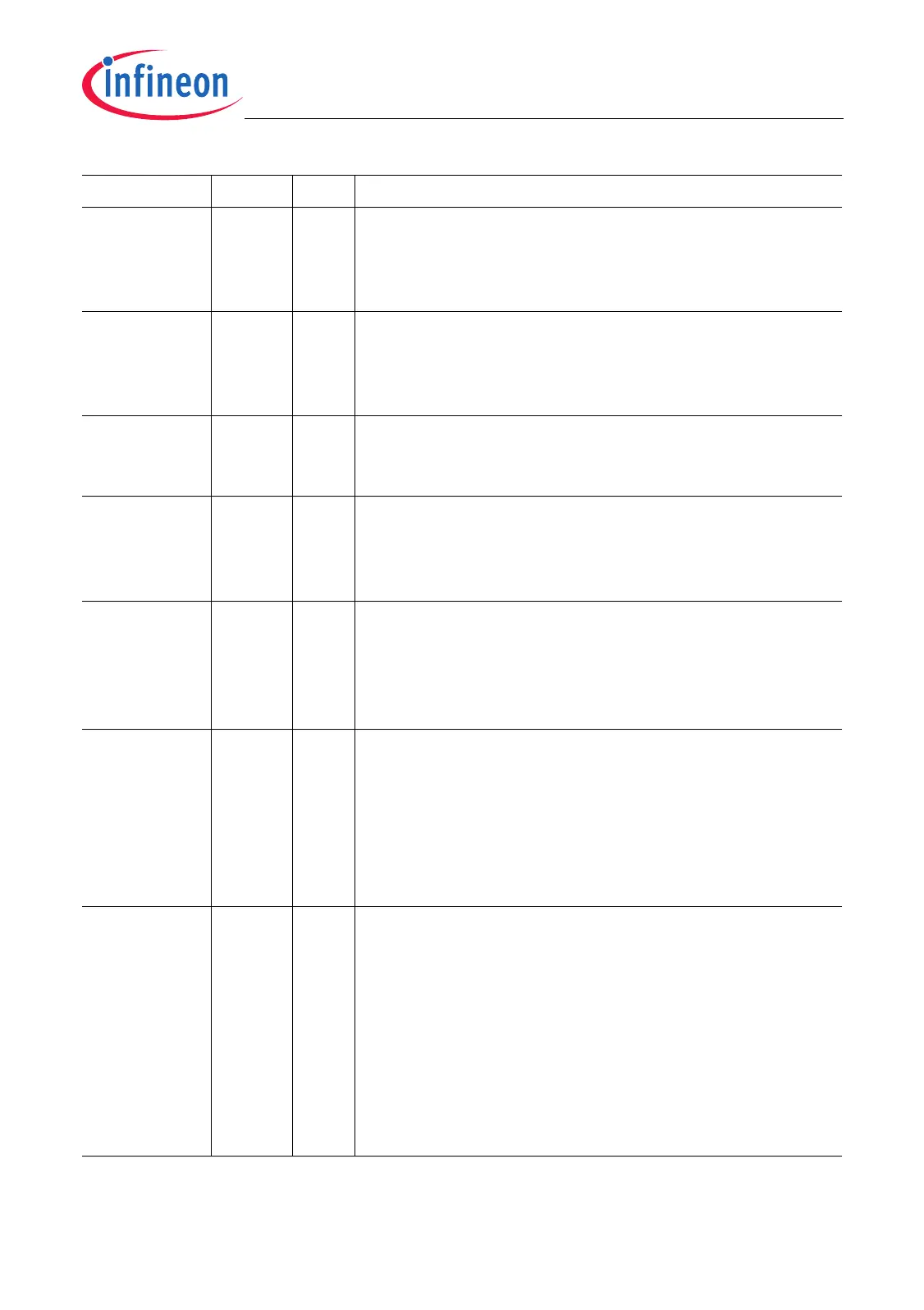

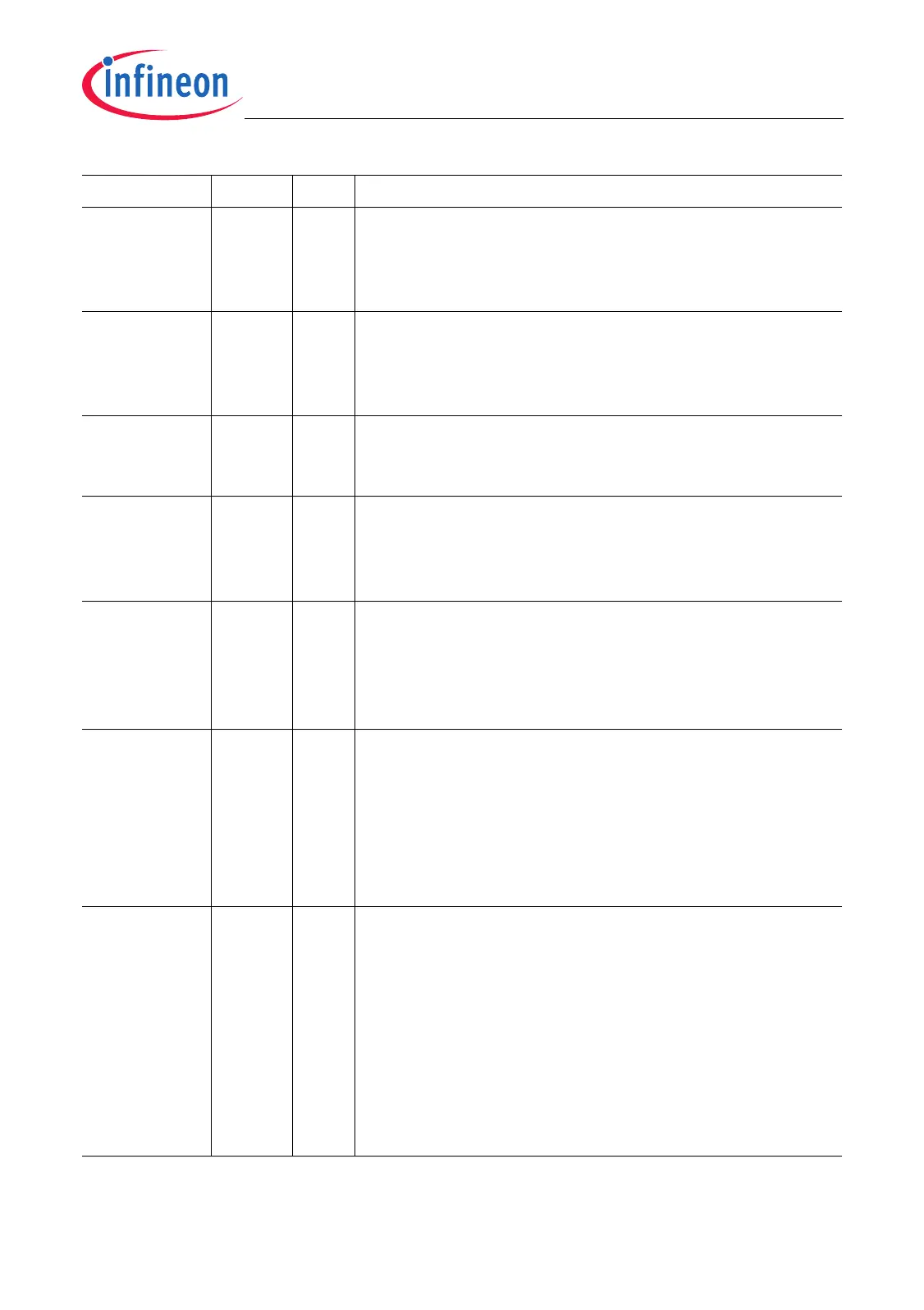

PEN 4rwILM = 1: LTC Prescaler Enable

0

B

LTC Prescaler Mode is disabled.

1

B

LTC Prescaler Mode with LTC prescaler clock

LTCPRE is enabled.

FED 5rwILM = 0: Input Falling Edge Select

0

B

Timer is not updated by a falling edge.

1

B

Timer is updated by a falling edge on the LTCkIN

input line.

AIL 5rwILM = 1: Active Input Level Select

0

B

Input signal is active high.

1

B

Input signal is active low.

SLO 6rwhSelect Line Output

0

B

State of select line output SO is 0.

1

B

State of select line output SO is 1.

SLO is bit protected (see Page 24-155).

CUDCLR 7wCoherent Update Disable

0

B

No effect.

1

B

Coherent update disabled (bit CUD is cleared).

If bits CUD and CUDCLR are both written with 1, bit

CUD will be set. CUDCLR is always read as 0.

ILM 8rwInput Line Mode

0

B

Input line is operating in Edge Sensitive Mode.

1

B

Input line is operating in Level Sensitive Mode.

In case of full speed GPTA module clock selection as

input clock, Level Sensitive Mode must be selected. In

this case the Edge Sensitive Mode will not produce any

event.

CUD 9rwhCoherent Update Enable

0

B

Select output SO is not toggled on timer reset

overflow.

1

B

Select output SO is toggled on next timer reset

overflow.

When CUD is set by software (writing CUD and

CUDCLR both with 1), it remains set until the next timer

reset overflow (LTCk reset event) occurs and is cleared

by hardware afterwards. CUD can be cleared by

software by writing bit CUDCLR with 1 and CUD with 0.

Field Bits Type Description

Loading...

Loading...