TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-188 V2.0, 2007-07

GPTA, V2.0

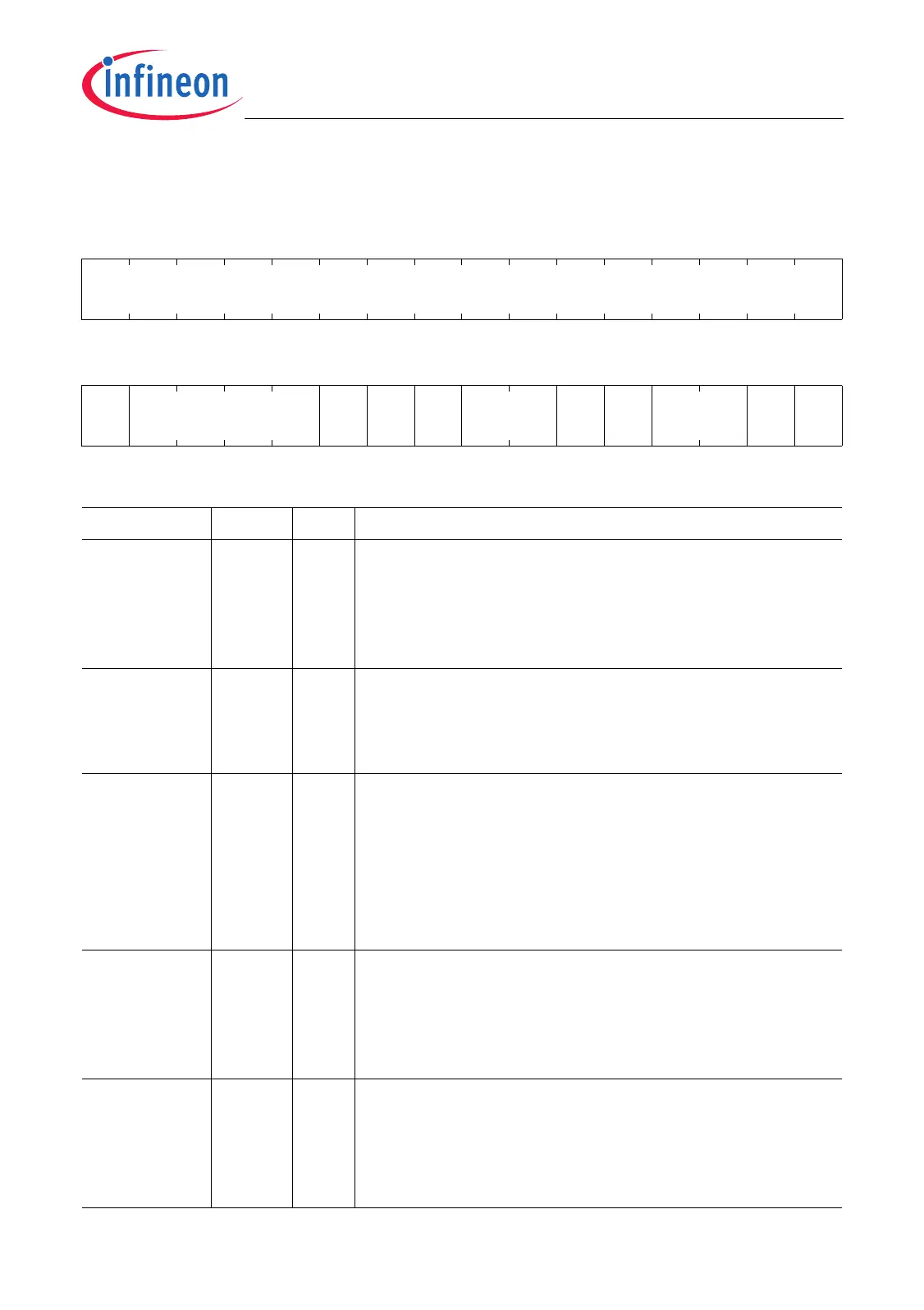

LTCCTR63

Local Timer Cell Control Register 63 (3F8

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

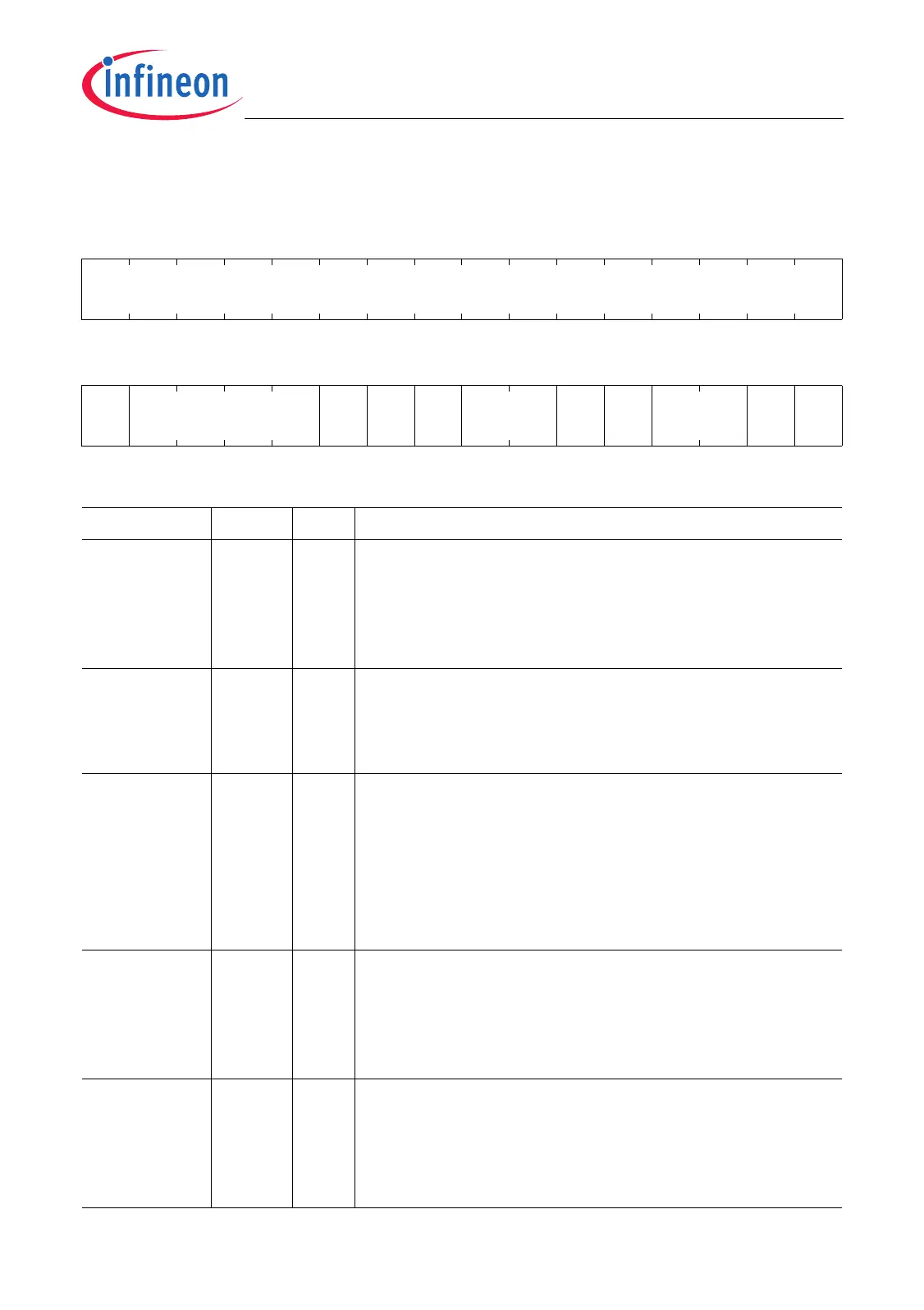

1514131211109876543210

OUT 0 CEN 0 ILM 0 FED RED REN OSM BRM

rh r rh r rw r rw rw rw rw rw

Field Bits Type Description

BRM 0rwBit Reversal Mode Control

0

B

Compare uses normal sequence of local input

data bus (YI) bits.

1

B

Compare uses reversed sequence of local input

data bus (YI) bits.

OSM 1rwOne Shot Mode Enable for Shadow Register Copy

0

B

Shadow register copy is continuously enabled.

1

B

Shadow register copy is enabled for one event

only.

REN [3:2] rw Request Enable

00

B

Service request SQT63 is disabled.

01

B

Service request SQT63 is generated when a

compare event has occurred.

10

B

Service request SQT63 is generated when a

shadow register copy event has occurred.

11

B

Reserved.

RED 4rwRising Edge Select for Shadow Register Copy

0

B

Shadow register copy is not triggered by a rising

edge on the LTC63IN input line.

1

B

Shadow register copy is triggered by a rising

edge on the LTC63IN input line.

FED 5rwFalling Edge Select for Shadow Register Copy

0

B

Shadow register copy is not triggered by a falling

edge on the LTC63IN input line.

1

B

Shadow register copy is triggered by a falling

edge on the LTC63IN input line.

Loading...

Loading...