TC1796

System Units (Vol. 1 of 2)

System Control Unit

User’s Manual 5-26 V2.0, 2007-07

SCU, V2.0

The Interrupt Gating Control Registers IGCR0 and IGCR1 contain bits to enable the

pattern detection and to control the gating for output channel 0 to 3 (e.g. for interrupt

nodes or peripherals).

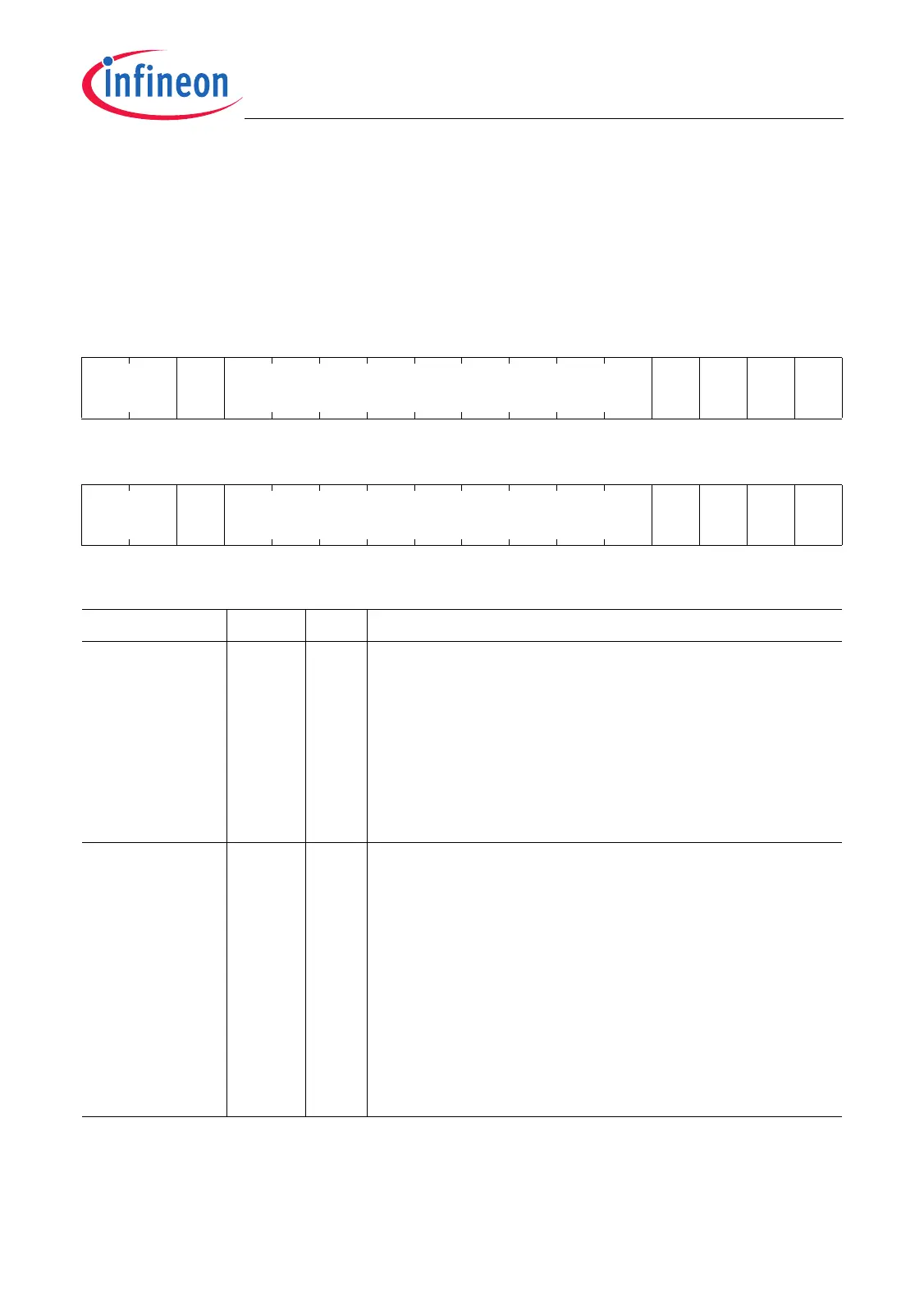

IGCR0

Interrupt Gating Register 0 (F0000094

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

IGP1

GE

EN1

0

IPEN

13

IPEN

12

IPEN

11

IPEN

10

rw rw r rw rw rw rw

1514131211109876543210

IGP0

GE

EN0

0

IPEN

03

IPEN

02

IPEN

01

IPEN

00

rw rw r rw rw rw rw

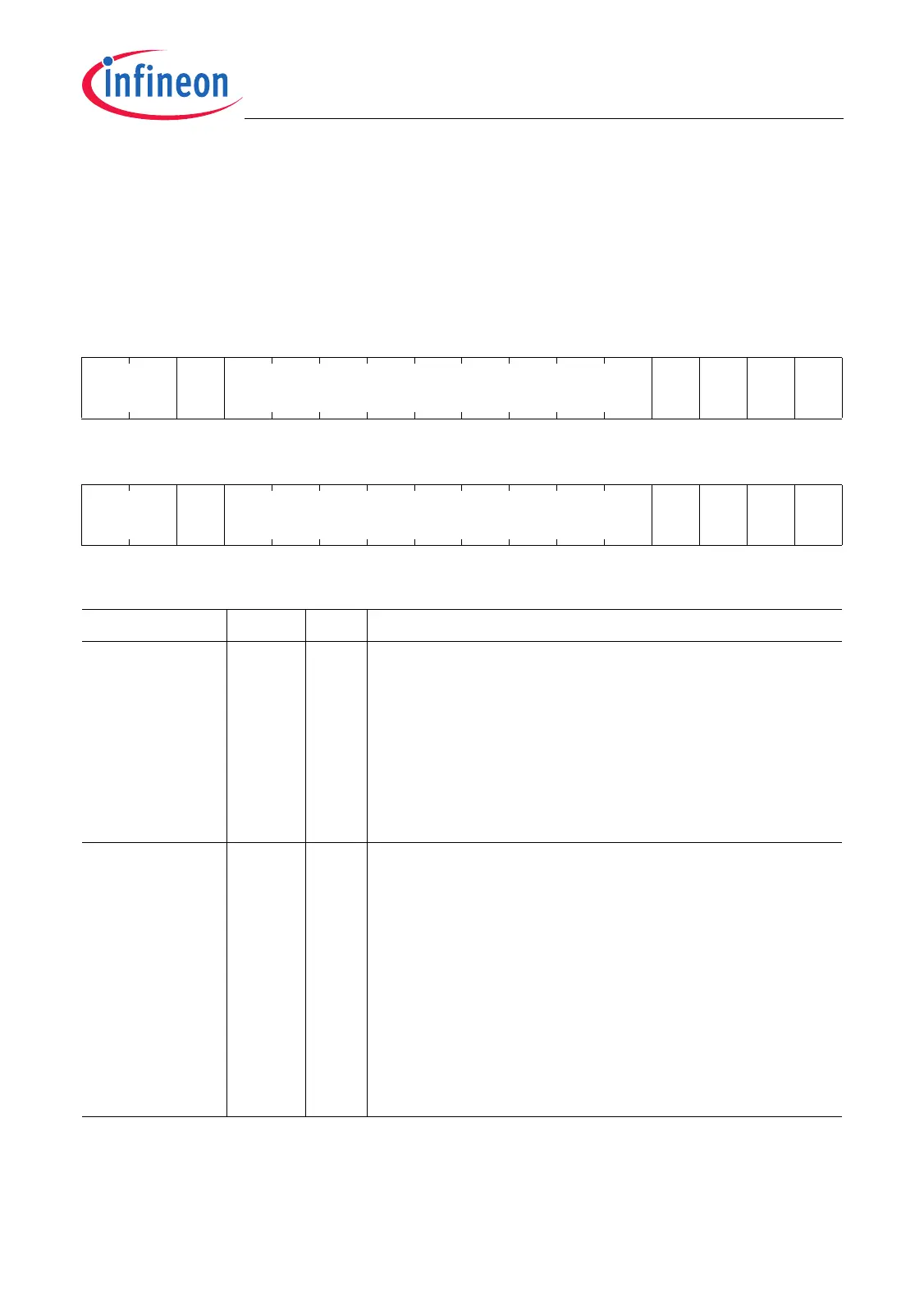

Field Bits Type Description

IPEN0x

(x = 0-3)

xrwInterrupt Pattern Enable for Channel 0

Bit IPEN0x determines the flag INTFx of channel x

takes part in the pattern detection for the gating of the

requests for the output signals GOUTy and IOUTy.

0

B

The bit INTFx does not take part in the pattern

detection.

1

B

The bit INTFx is taken into consideration for the

pattern detection.

GEEN0 13 rw Generate Event Enable 0

Bit GEEN0 enables the generation of a trigger event

for output channel 0 when the result of the pattern

detection changes. When using this feature, a trigger

(e.g. for an interrupt) is generated during the first

clock cycle when a pattern is detected or when it is no

longer detected.

0

B

The trigger generation at a change of the

pattern detection result is disabled.

1

B

The trigger generation at a change of the

pattern detection result is enabled.

Loading...

Loading...