TC1796

System Units (Vol. 1 of 2)

System Control Unit

User’s Manual 5-52 V2.0, 2007-07

SCU, V2.0

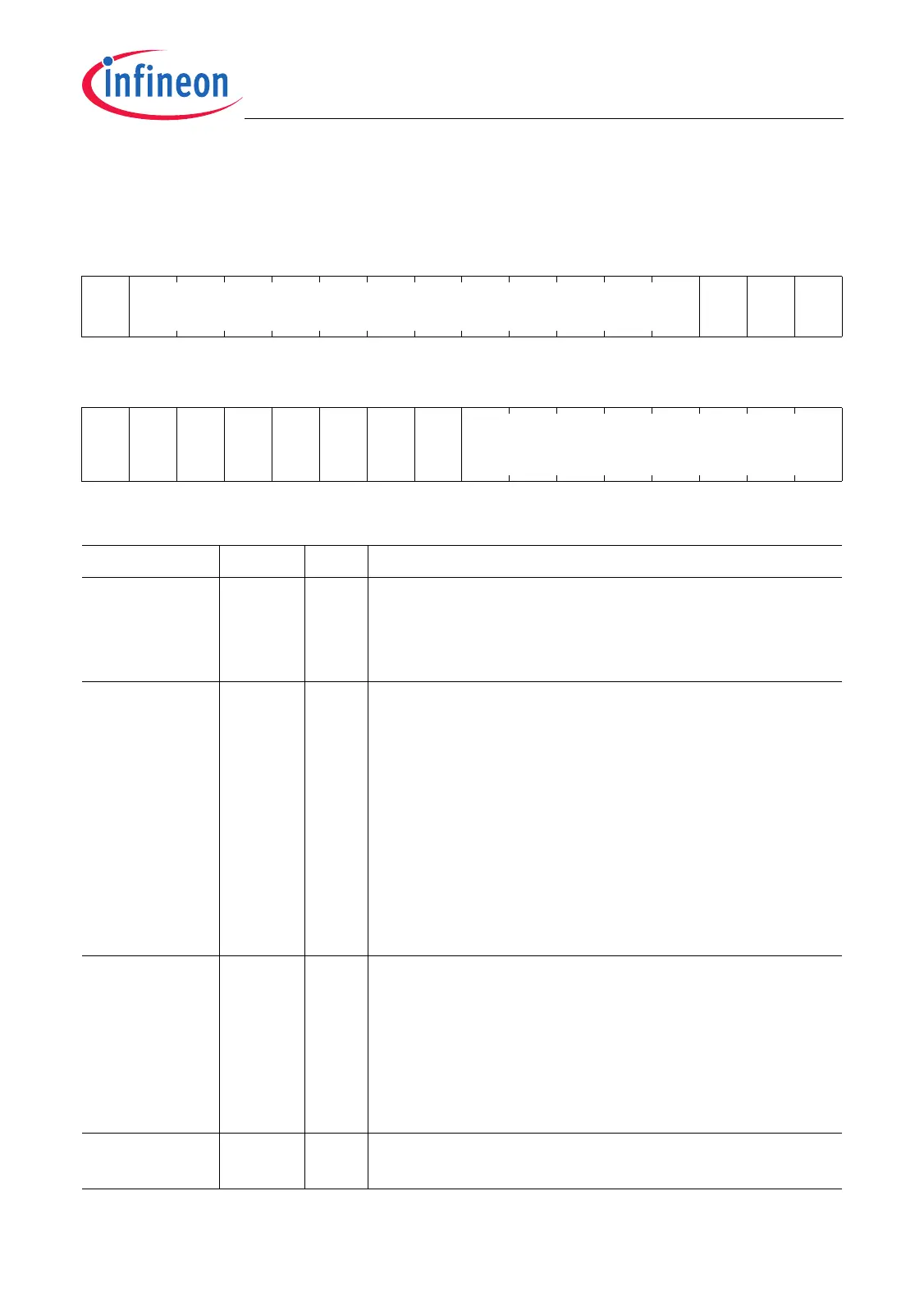

SCU_PTCON

SCU Pad Test Control Register (F00000B0

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PTM

EN

0000

rh r rw rw rw

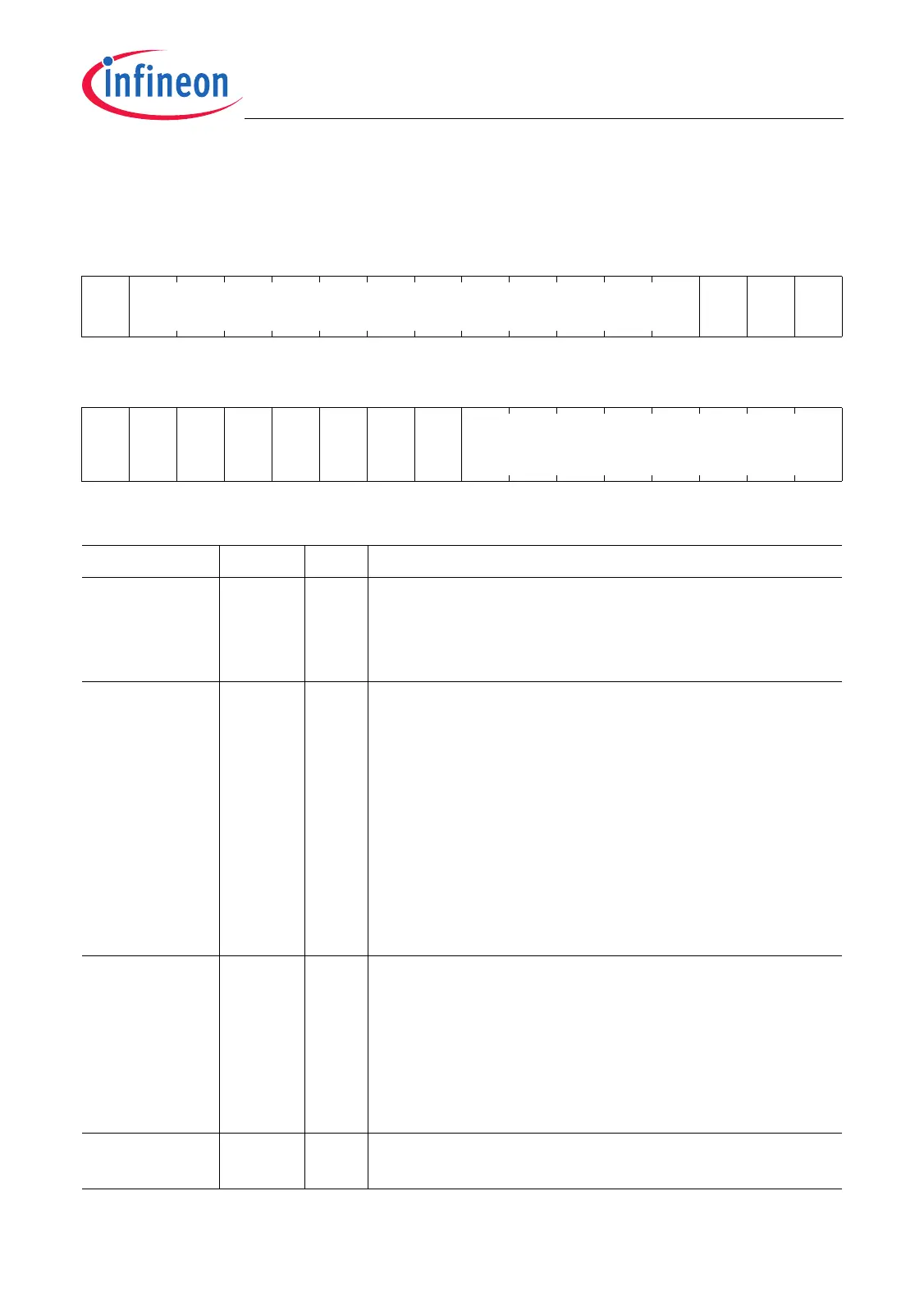

1514131211109876543210

RD

SS3

RD

SS2

RD

SS1

RD

SS0

EN

OUT

3

EN

OUT

2

EN

OUT

1

EN

OUT

0

PTMLC

rw rw rw rw rw rw rw rw w

Field Bits Type Description

PTMLC [7:0] w Pad Test Mode Lock Code

This bit field must be written with a special two-word

write sequence to enable the pad test mode.

PTMLC is always read as 00

H

.

ENOUTn

(n = 0-3)

n+8 rw Enable Data Output for Pad Test Data Register n

In pad test mode (PTMEN = 1), these bits determine

whether or not the logic level state as defined by the

bits in the SCU_PTDATn register is switched as

inverted state to the pad/pin.

0

B

Pad drivers of the pad test data register n

related pads are disabled.

1

B

Pad drivers of the pad test data register n

related pads are enabled and the bits in the pad

test data register n are output as inverted state

at the related pins.

RDSSn

(n = 0-3)

n+12 rw Read Source Selection for Pad Test Data

Register n

In pad test mode (PTMEN = 1), these bits determine

the read source for the SCU_PTDATn register.

0

B

Logic levels of the pad test data register n

related pads/pins are read.

1

B

Pad test data register n bits are read.

0 16 rw Reserved

Read as 0 after reset; returns the value that is written.

Loading...

Loading...