TC1796

System Units (Vol. 1 of 2)

System Control Unit

User’s Manual 5-53 V2.0, 2007-07

SCU, V2.0

Note: In pad test mode, the bits in SCU_PTDAT0 are output to the pad/pin in inverted

state: a 0 generates a high level and a 1 generates a low level at the pad/pin.

0 17, 18 rw Reserved

Read as 0; bits must be written with 0.

PTMEN 31 rh Pad Test Mode Enable Flag

0

B

Pad test mode disabled (default after reset)

1

B

Pad test mode enabled

0 [30:19] r Reserved

Read as 0; should be written with 0.

SCU_PTDAT0

SCU Pad Test Data Register 0 (F00000B4

H

) Reset Value: XXXX XXXX

H

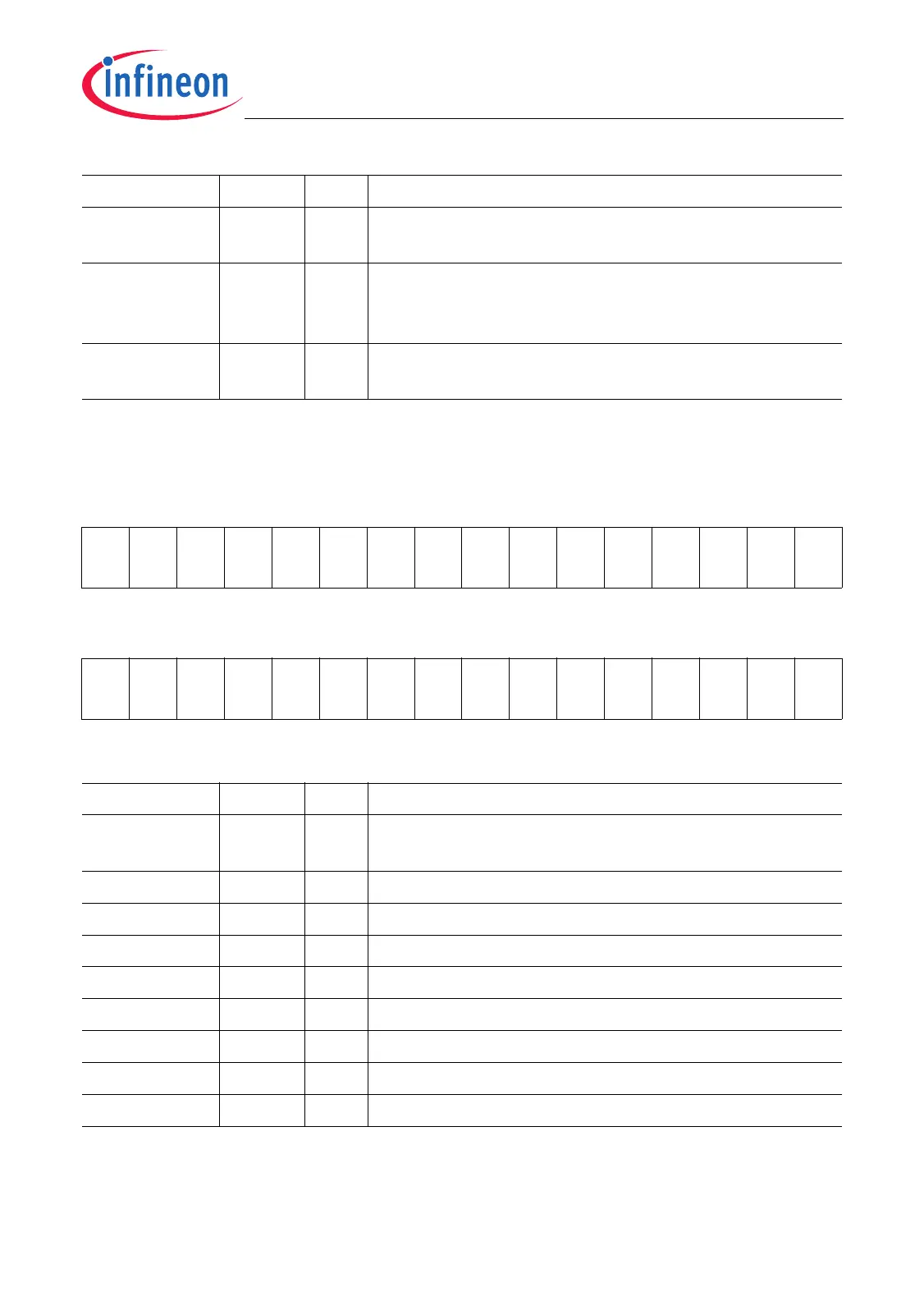

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

MR

W

ADV

RD

WR

RD BC3 BC2 BC1 BC0 A23 A22 A21 A20 A19 A18 A17 A16

rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh

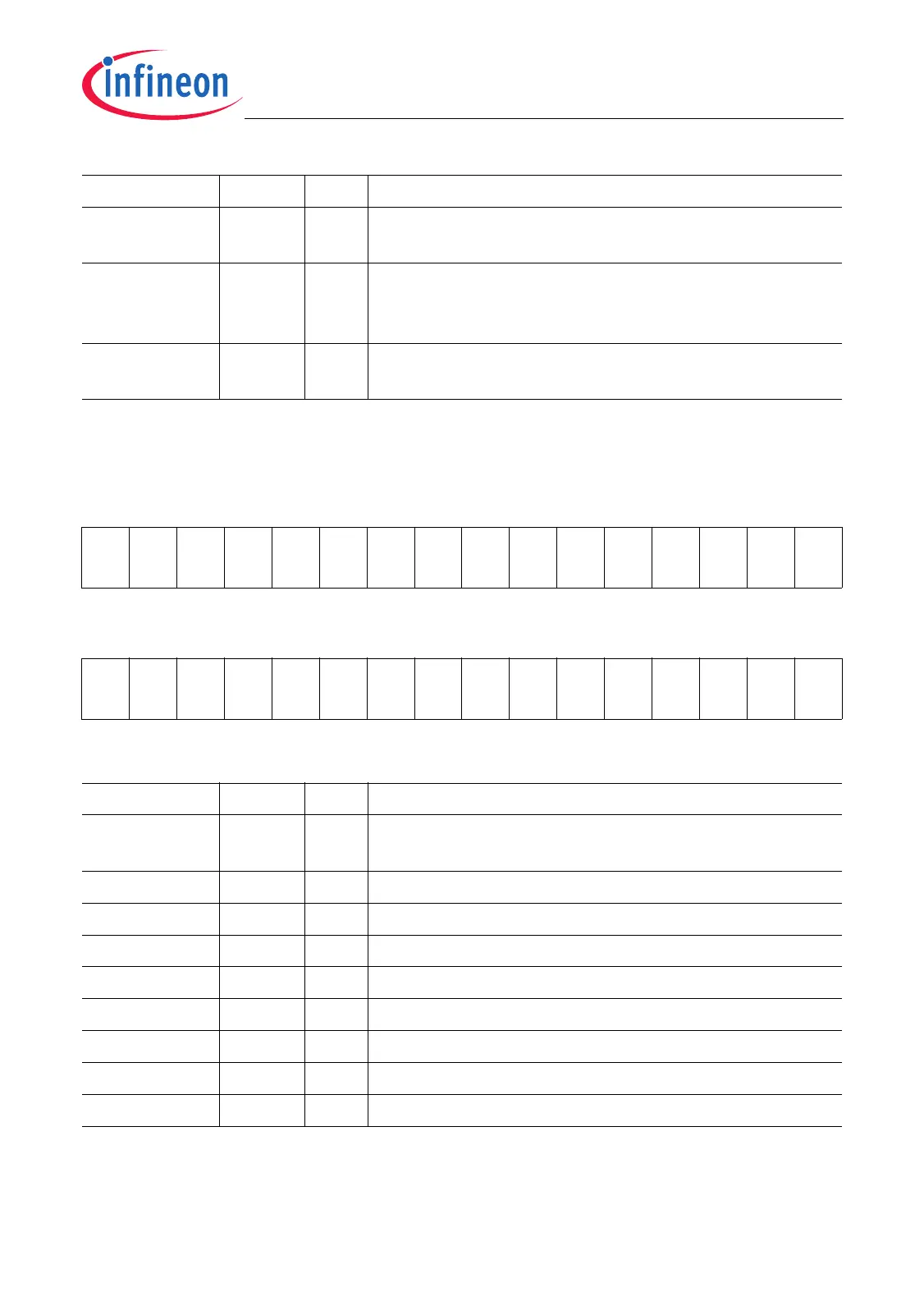

1514131211109876543210

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh rwh

Field Bits Type Description

An

(n = 0-23)

nrwhPad Test Value for/of EBU Address Bus Line An

BC0 24 rwh Pad Test Value for/of BC0

BC1 25 rwh Pad Test Value for/of BC1

BC2 26 rwh Pad Test Value for/of BC2

BC3 27 rwh Pad Test Value for/of BC3

RD 28 rwh Pad Test Value for/of RD

RDWR 29 rwh Pad Test Value for/of RD/WR

ADV 30 rwh Pad Test Value for/of ADV

MRW 31 rwh Pad Test Value for/of MR/W

Field Bits Type Description

Loading...

Loading...