TC1796

System Units (Vol. 1 of 2)

Introduction

User’s Manual 1-25 V2.0, 2007-07

Intro, V2.0

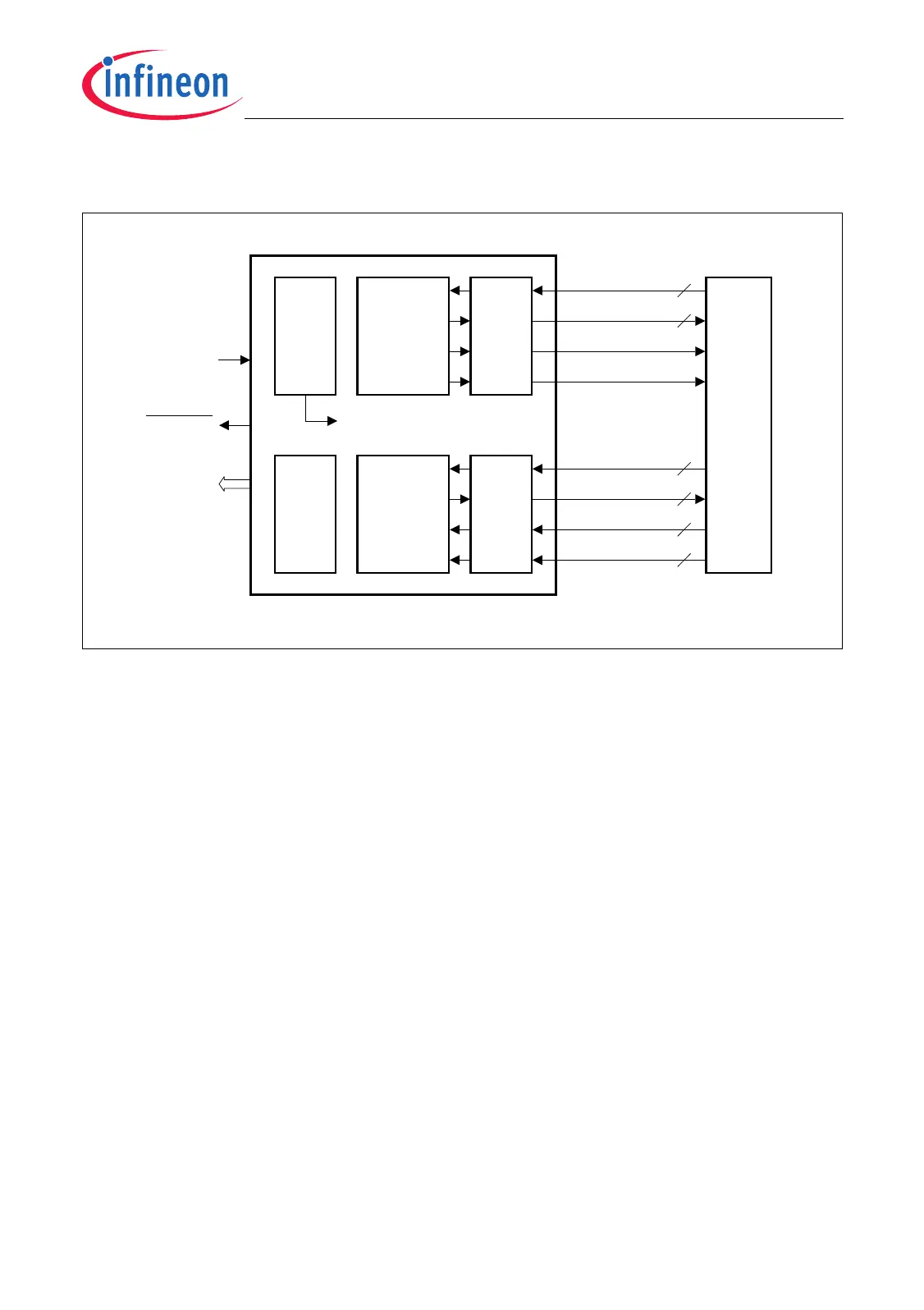

Figure 1-7 shows a general block diagram of the MLI Module.

Figure 1-7 General Block Diagram of the MLI Module

The MLI transmitter and MLI receiver communicate with other off-chip MLI receivers and

MLI transmitters via a four-line serial I/O bus each. Several I/O lines of these I/O buses

are available outside the MLI module kernel as four-line output or input buses with index

numbering A, B, C and D. The transmitter signals are named with the prefix “T” and the

receiver signals are named with the prefix “R”.

Data read and write operations from/to remote window areas can be handled by a Move

Engine that is able to operate as a bus master. Clock control, address decoding, and

interrupt service request control are managed outside the MLI module kernel. Eight

service request outputs can be used to trigger an interrupt or a DMA request.

MCB05870_mod

Port

Control

SR[7:0]

TREADY[D:A]

TVALID[D:A]

RCLK[D:A]

TDATA

TCLK

RREADY[D:A]

RVALID[D:A]

RDATA[D:A]

Fract .

Divider

Move

Engine

f

ML I

BRKOUT

MLI

Transmitter

MLI

Receiver

MLI Module

I/O

Control

I/O

Control

4

4

4

4

4

4

f

SYS

Loading...

Loading...