TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-9 V2.0, 2007-07

DMA, V2.0

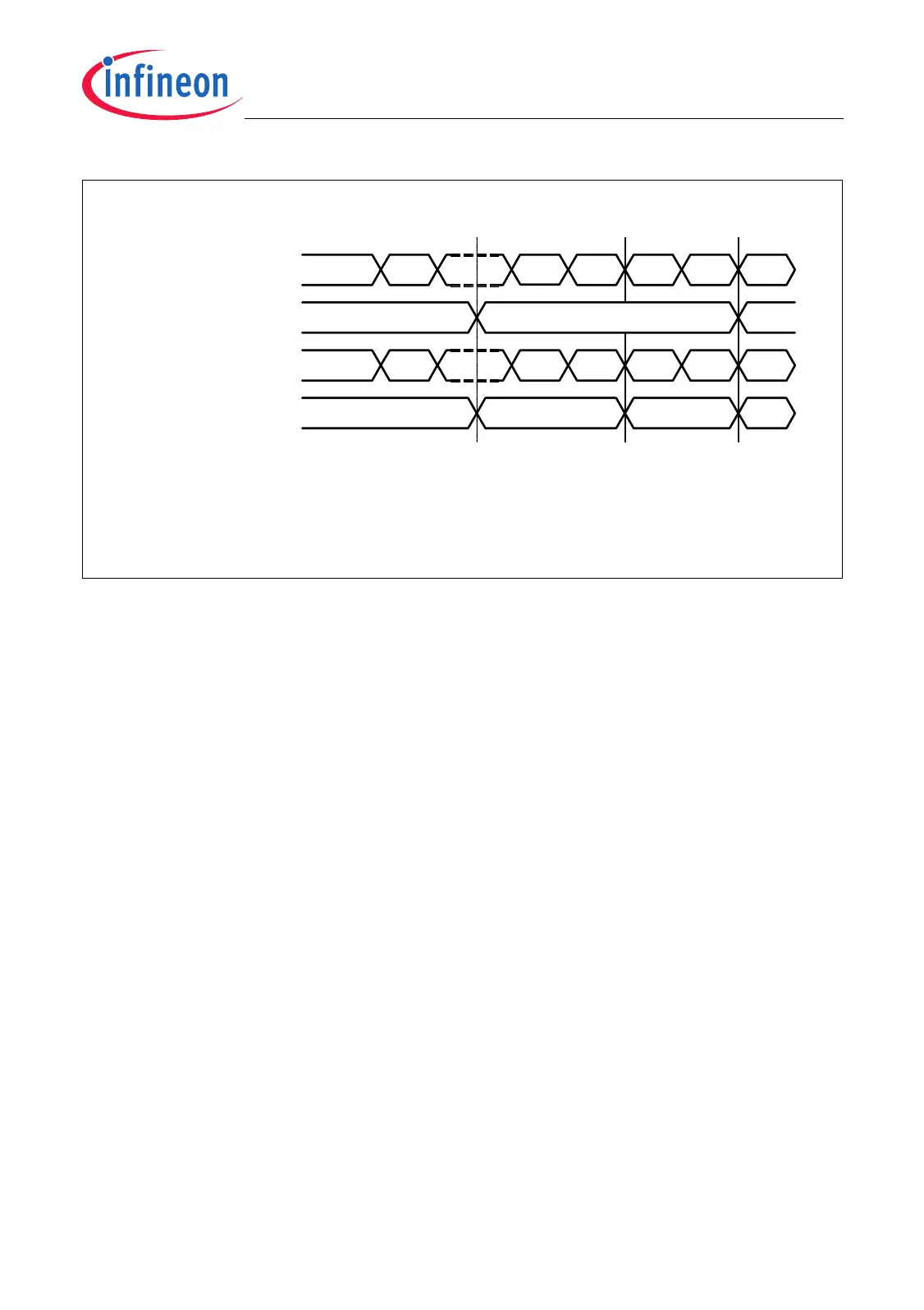

Figure 12-5 Shadow Source Address and Transfer Count Update

Figure 12-5 shows how the contents of the source address register SADRmn and the

transfer count CHSRmn.TCOUNT are updated during two DMA transactions with a

shadowed source address and transfer count update.

At reference point 2) the DMA transaction 1 is finished and DMA transaction 2 is started.

At 1) the DMA channel is reprogrammed with two new parameters for the next DMA

transaction: Transfer count tc2 and source address sa2. Source address sa2 is buffered

in SADRmn and transferred to SADRmn when the new DMA transaction is started at 2).

At this time, transfer count tc2 is also transferred to CHSRmn.TCOUNT.

tc2

MCT05684_mod

CHSRmn.TCOUNT

tc1 = transfer count 1

tc2 = transfer count 2

sa1 = source address 1

sa2 = source address 2

SHADRmn with

ADRCR0n.SHCT = 01

B

SADRmn

tc1 0

1

tc1-1 tc2 tc2-1 tc2-2

tc1

tc3

sa1

sa1+1 sa2+1 sa2+2sa2

tc1-1

sa1+

tc1

sa1+

sa2 sa3

CHCRmn.TREL

1) 3)2)

1) 3) = writing to CHCRmn and SADRmn

2) = start of new DMA transaction with

shadow transfer of source address

0000 0000

H

Loading...

Loading...