TC1796

System Units (Vol. 1 of 2)

LMB External Bus Unit

User’s Manual 13-56 V2.0, 2007-07

EBU, V2.0

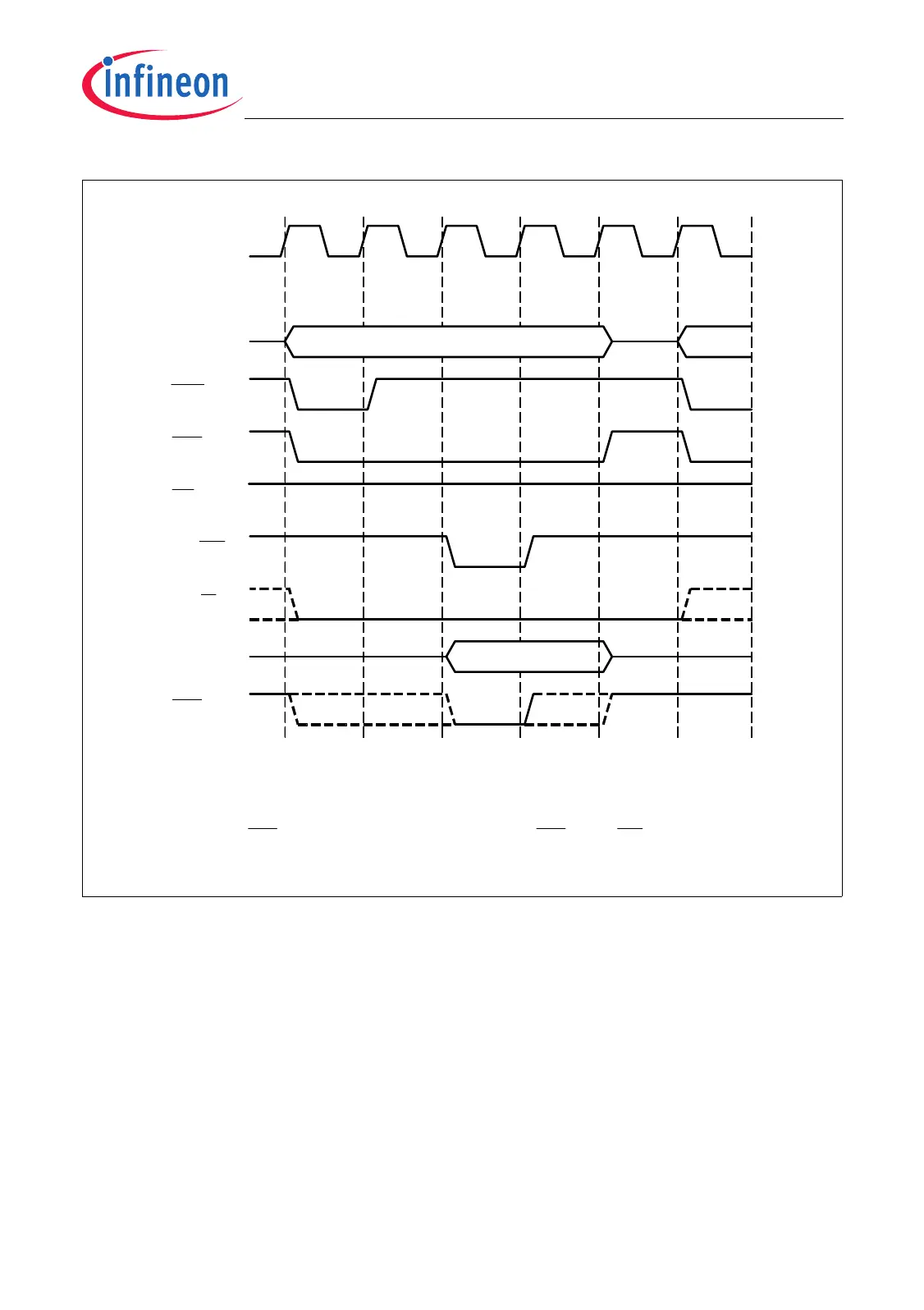

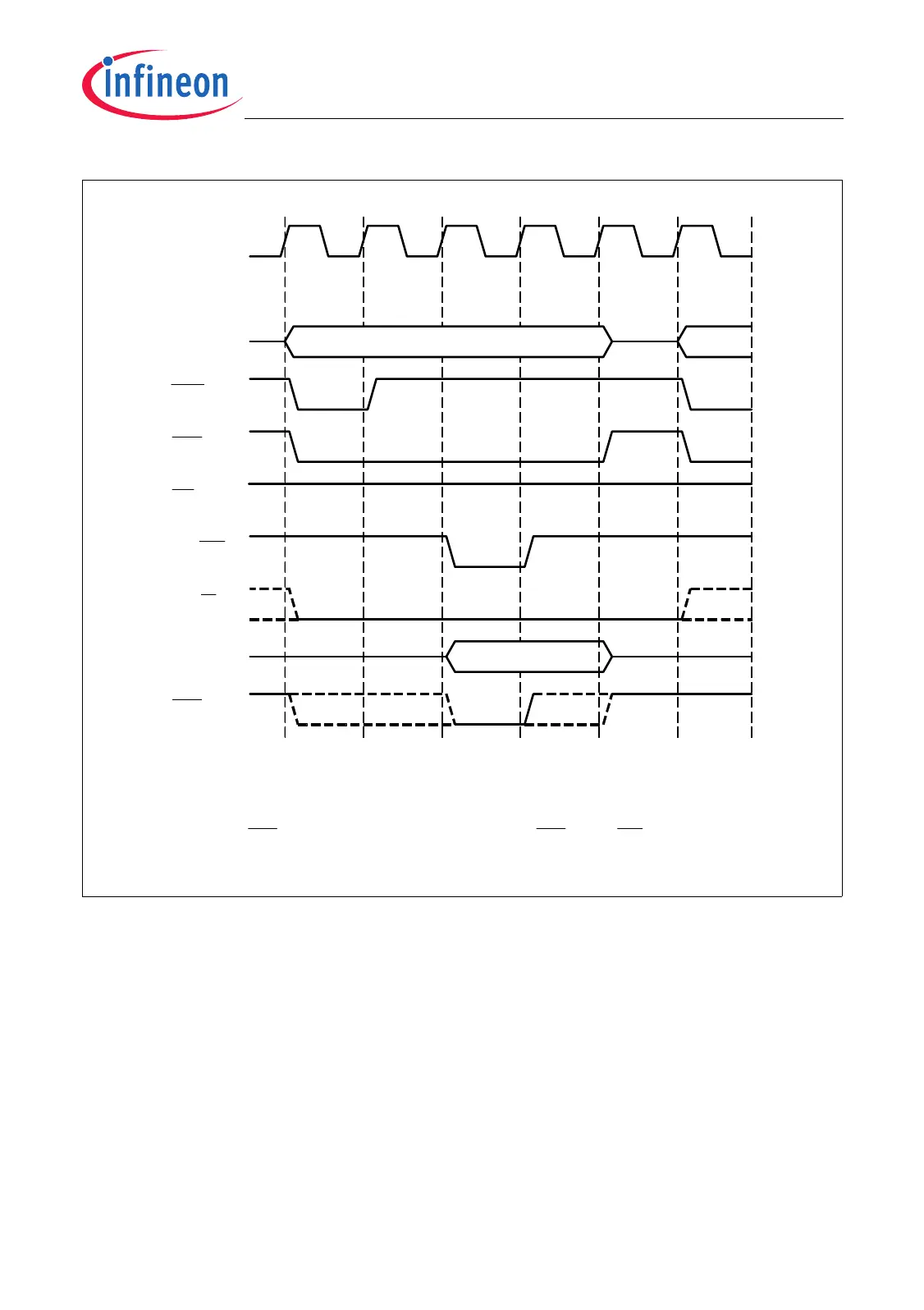

Figure 13-19 Demultiplexed External Bus Write Access Cycle

Figure 13-19 above shows an example of a write access to a demultiplexed device. This

type of access cycle consists of two to five phases as follows:

• Address Phase (compulsory)

• Command Delay Phase (optional)

• Command Phase (compulsory)

• Data Hold Phase (optional)

• Recovery Phase (optional)

The example shows an access cycle with all five phases programmed for a duration of

one LMBCLK cycle.

1) All phases programmed to one LMBCLK period length.

2) These phases are optional and can be skipped.

3) BCx signals can be asserted either with CSx or RD/WR.

LMBCLK

1)

A[23:0]

Address

ADV

AP

(1 to n)

CD

2)

(0 to n)

CP

(1 to n)

DH

2)

(0 to n)

next AP

Next. A.

CSx

RD

RD/WR

MR/W

Data out

D[31:0]

BCx

3) 3)

RP

2)

(0 to n)

MCT05730

Notes:

Loading...

Loading...