www.ti.com

N2HET Control Registers

1021

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

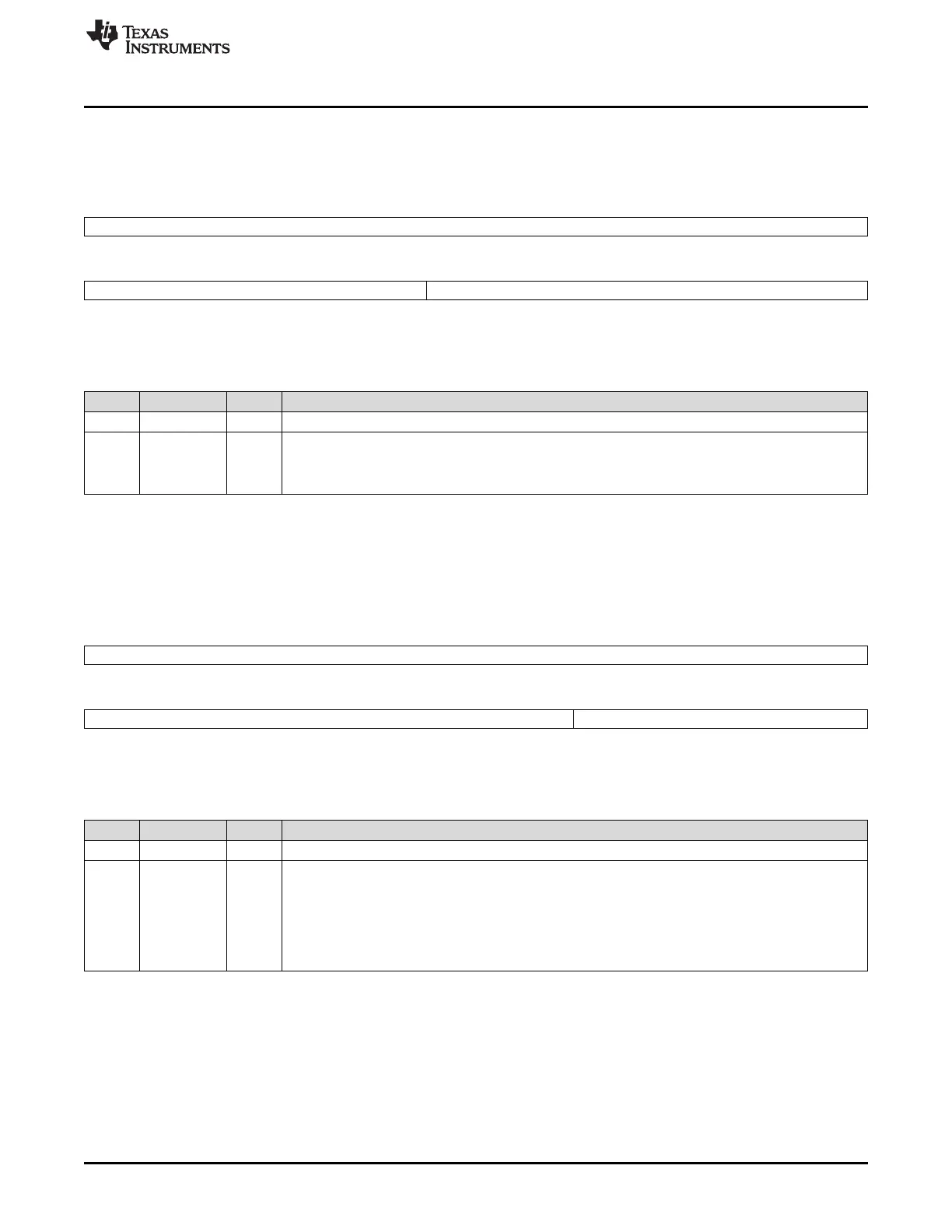

23.4.3 N2HET Current Address Register (HETADDR)

N2HET1: offset = FFF7 B808h; N2HET2: offset = FFF7 B908h

Figure 23-58. N2HET Current Address (HETADDR)

31 16

Reserved

R-0

15 9 8 0

Reserved HETADDR

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 23-18. N2HET Current Address (HETADDR) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reads return 0. Writes have no effect.

8-0 HETADDR N2HET Current Address

Read: Returns the current N2HET program address.

Write: Writes have no effect.

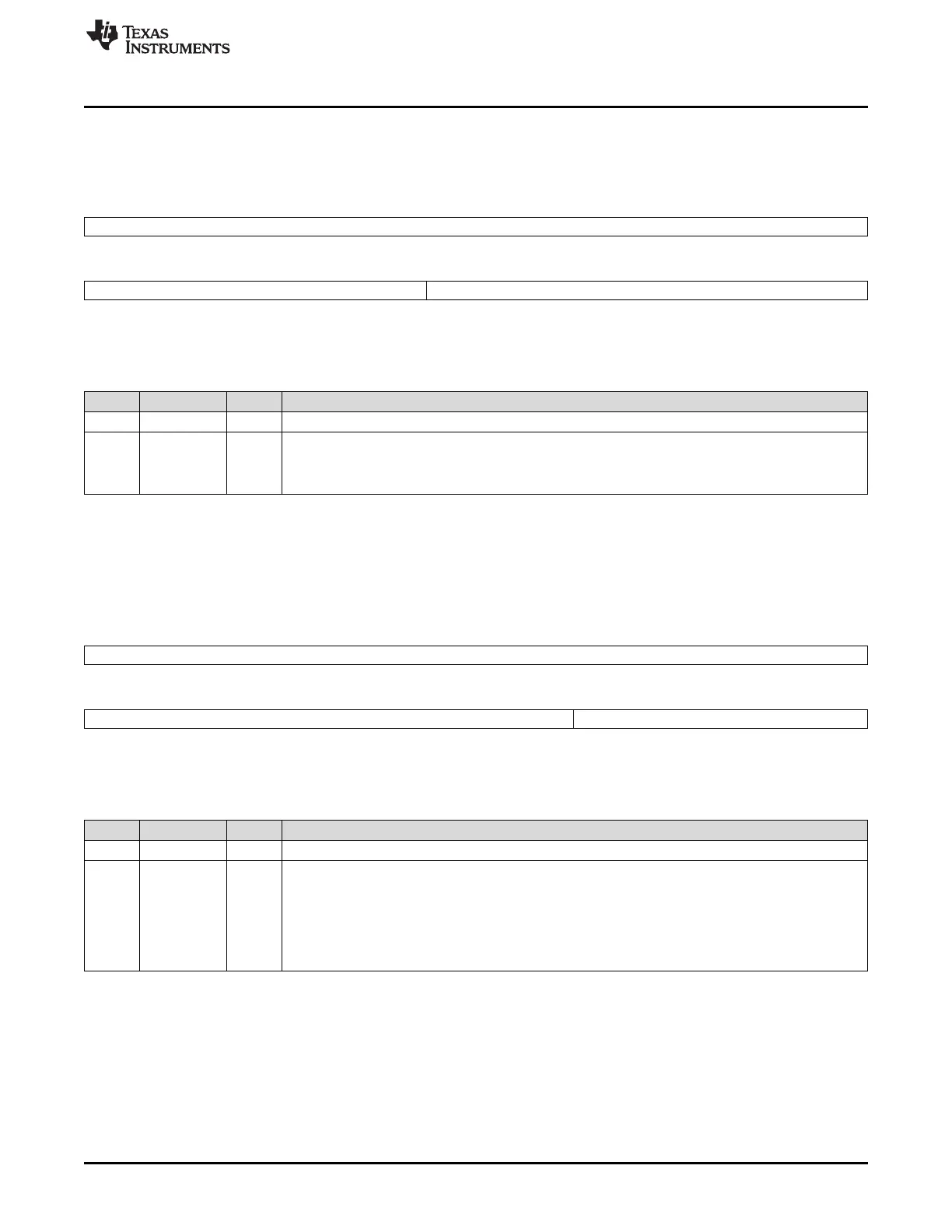

23.4.4 Offset Index Priority Level 1 Register (HETOFF1)

N2HET1: offset = FFF7 B80Ch; N2HET2: offset = FFF7 B90Ch

Figure 23-59. Offset Index Priority Level 1 Register (HETOFF1)

31 16

Reserved

R-0

15 6 5 0

Reserved OFFSET1

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 23-19. Offset Index Priority Level 1 Register (HETOFF1) Field Descriptions

Bit Field Value Description

31-6 Reserved 0 Reads return 0. Writes have no effect.

5-0 OFFSET1 OFFSET1 indexes the currently pending high-priority interrupt. Offset values and sources are listed in

Table 23-20.

Read: Read of these bits determines the pending N2HET interrupt.

Write: Writes have no effect.

Note: In any read operation mode, the corresponding flag (in the HETFLG) is also cleared. In Emulation

mode the corresponding flag is not cleared.

Loading...

Loading...