HTU Control Registers

www.ti.com

1164

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer Transfer Unit (HTU) Module

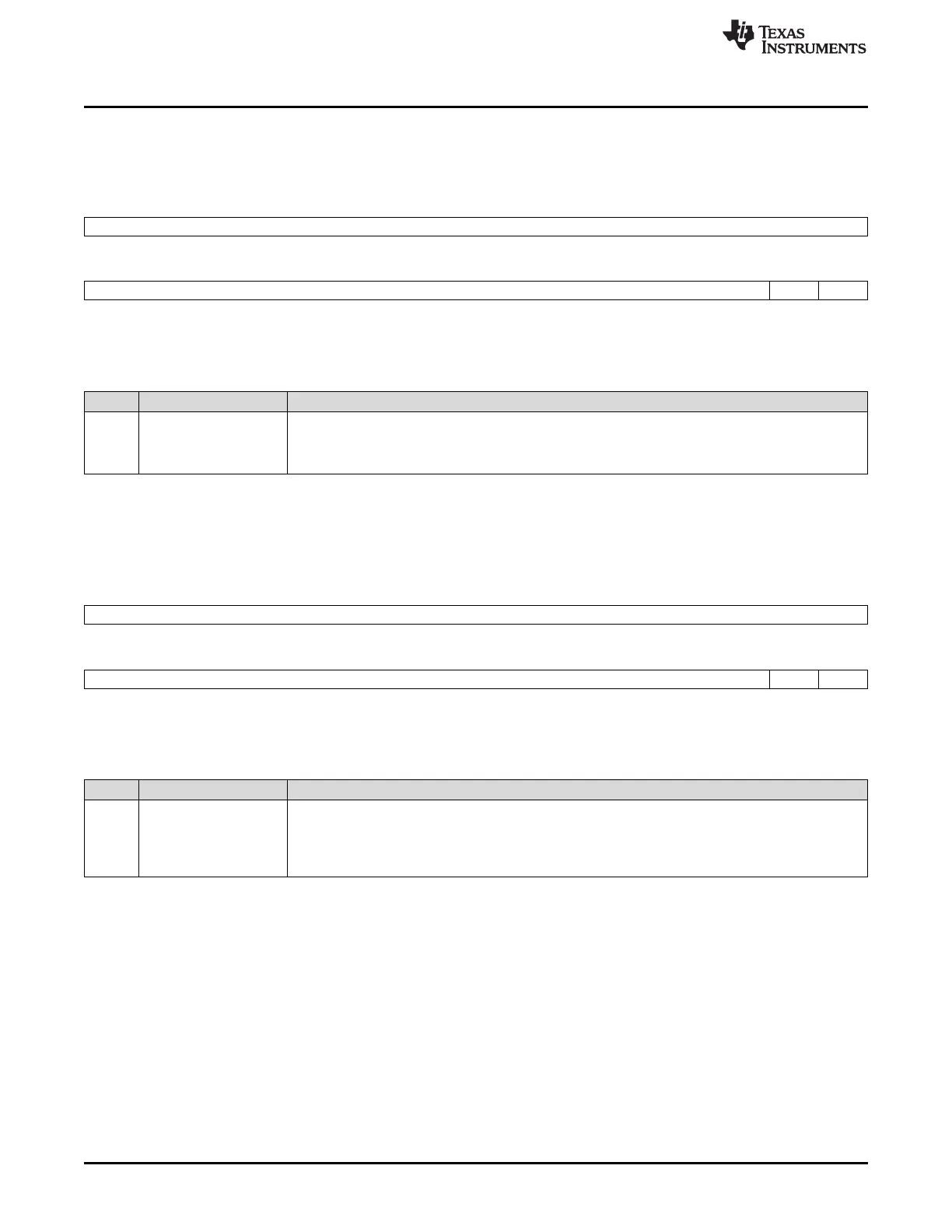

24.4.18 Memory Protection 1 Start Address Register (HTU MP1S)

This register configures the start address of memory protection region 1.

Figure 24-31. Memory Protection 1 Start Address Register (HTU MP1S) [offset = 4Ch]

31 16

STARTADDRESS1

R/WP-0

15 2 1 0

STARTADDRESS1 0 0

R/WP-0

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -n = value after reset

Table 24-31. Memory Protection 1 Start Address Register (HTU MP1S) Field Descriptions

Bit Field Description

31-0 STARTADDRESS1 The start address defines at which main memory address the region begins. A memory protection error

will be triggered, if the HTU accesses an address smaller than STARTADDRESS1 and the MPCS bit

REG01ENA register is configured accordingly. The address is 32-bit aligned, so the 2 LSBs are not

significant and will always read 0.

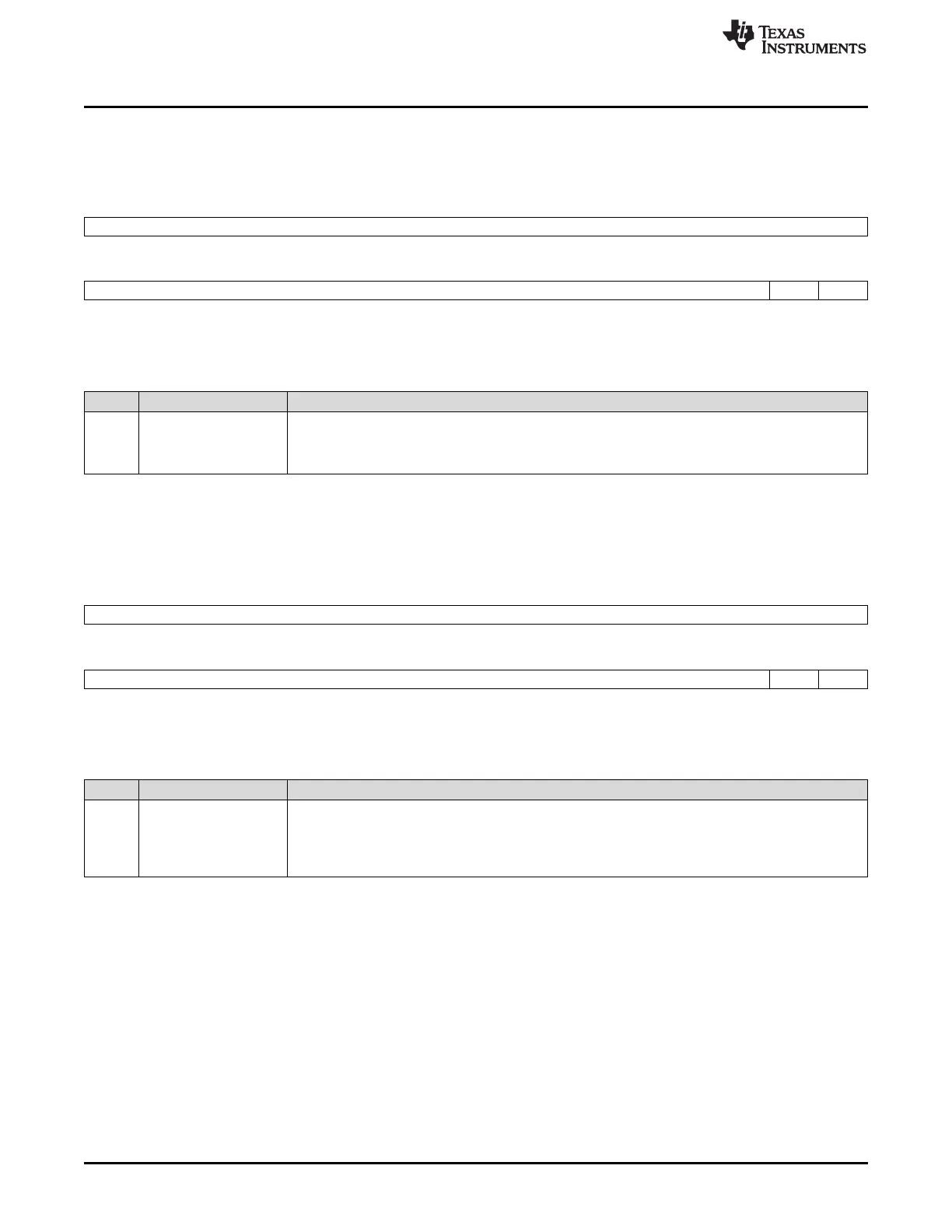

24.4.19 Memory Protection 1 End Address Register (HTU MP1E)

Figure 24-32. Memory Protection 1 End Address Register (HTU MP1E) [offset = 50h]

31 16

ENDADDRESS1

R/WP-0

15 2 1 0

ENDADDRESS1 0 0

R/WP-0

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -n = value after reset

Table 24-32. Memory Protection 1 End Address Register (HTU MP1E) Field Descriptions

Bit Field Description

31-0 ENDADDRESS1 The end address defines at which address the region ends. A memory protection error will be

triggered, if the HTU accesses an address bigger than ENDADDRESS1 and the register bit

REG01ENA is configured accordingly. The address is 32-bit aligned, so the 2 LSBs are not significant

and will always read 0. The effective end address is rounded up to the nearest word end address, that

is, 0x200 = 0x203.

Loading...

Loading...