www.ti.com

PBIST Control Registers

421

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Programmable Built-In Self-Test (PBIST) Module

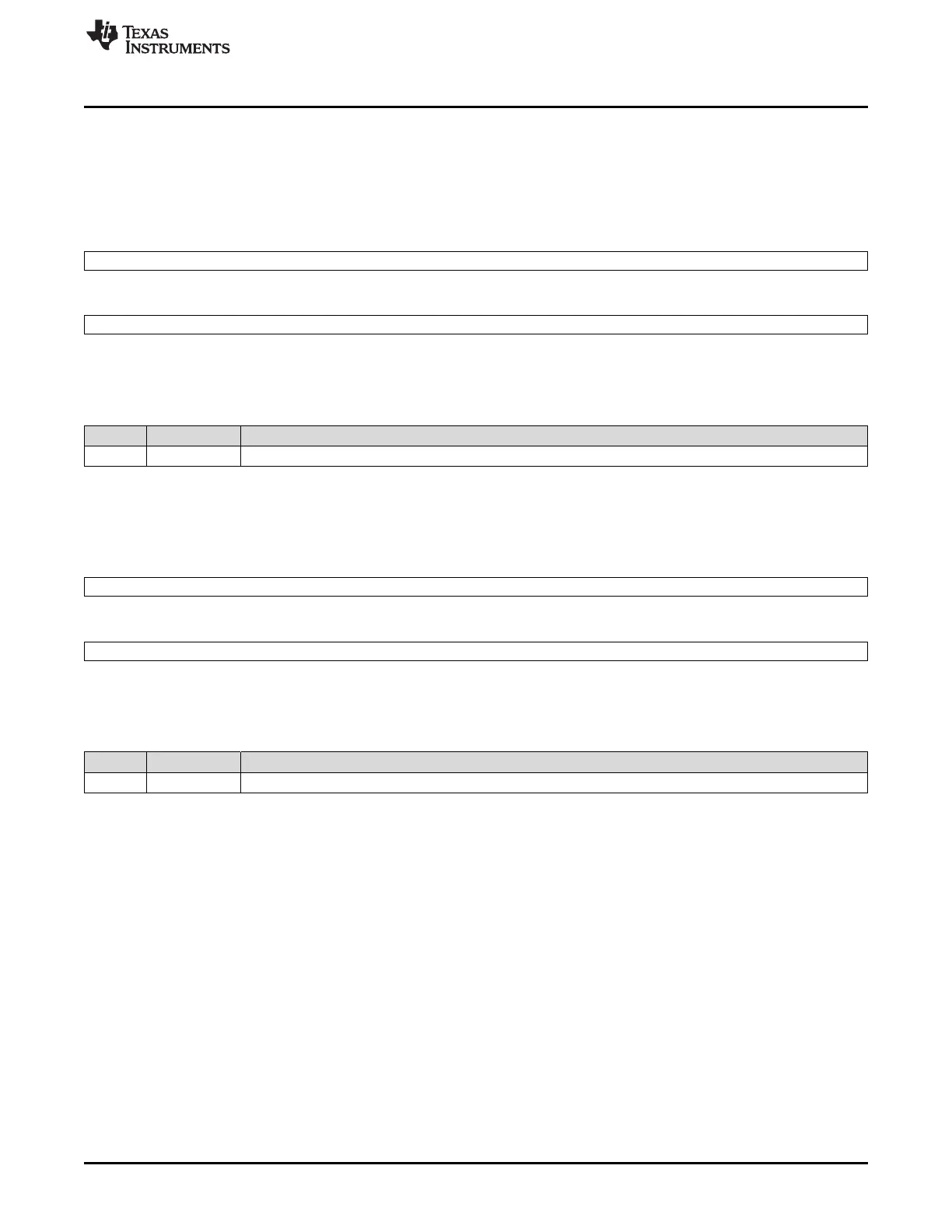

9.5.9 Fail Status Data Registers (FSRDL0 and FSRDL1)

These registers are used to capture the failure data in case of a memory self-test failure. FSRDL0

corresponds to Port 0, while FSRDL1 corresponds to Port 1. Figure 9-13 and Table 9-12 illustrate the

FSRDL0 register, while Figure 9-14 and Table 9-13 illustrate the FSRDL1 register.

Figure 9-13. Fail Status Data Register 0 (FSRDL0) [offset = 01A8h]

31 16

FSRDL0

R-AAAAh

15 0

FSRDL0

R-AAAAh

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 9-12. Fail Status Data Register 0 (FSRDL0) Field Descriptions

Bit Field Description

31-0 FSRDL0 Failure data on port 0.

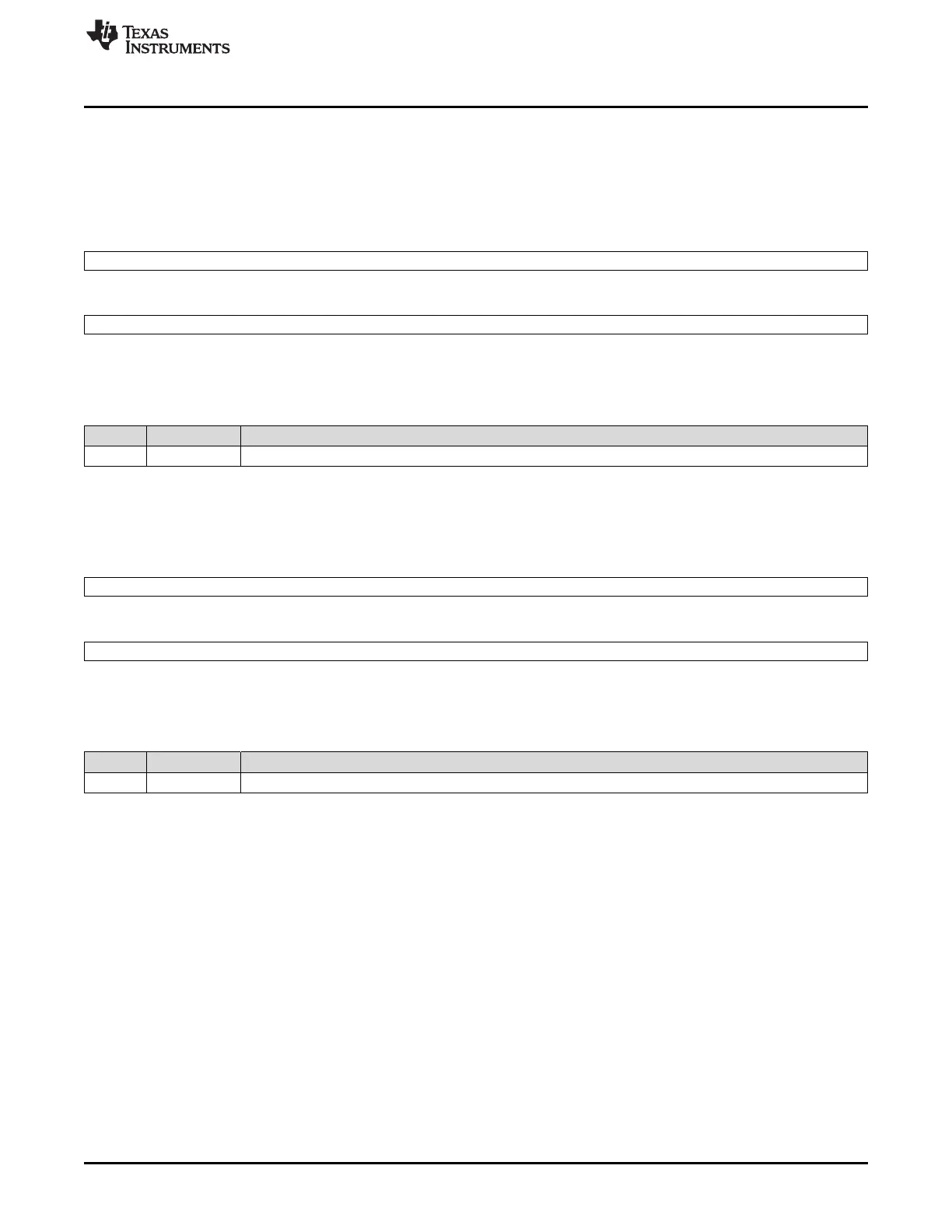

Figure 9-14. Fail Status Data Register 1 (FSRDL1) [offset = 01B0h]

31 16

FSRDL1

R-AAAAh

15 0

FSRDL1

R-AAAAh

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 9-13. Fail Status Data Register 1 (FSRDL1) Field Descriptions

Bit Field Description

31-0 FSRDL1 Failure data on port 1.

Loading...

Loading...