www.ti.com

SCM Registers

261

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

SCR Control Module (SCM)

3.4.2 SCM Control Register (SCMCNTRL)

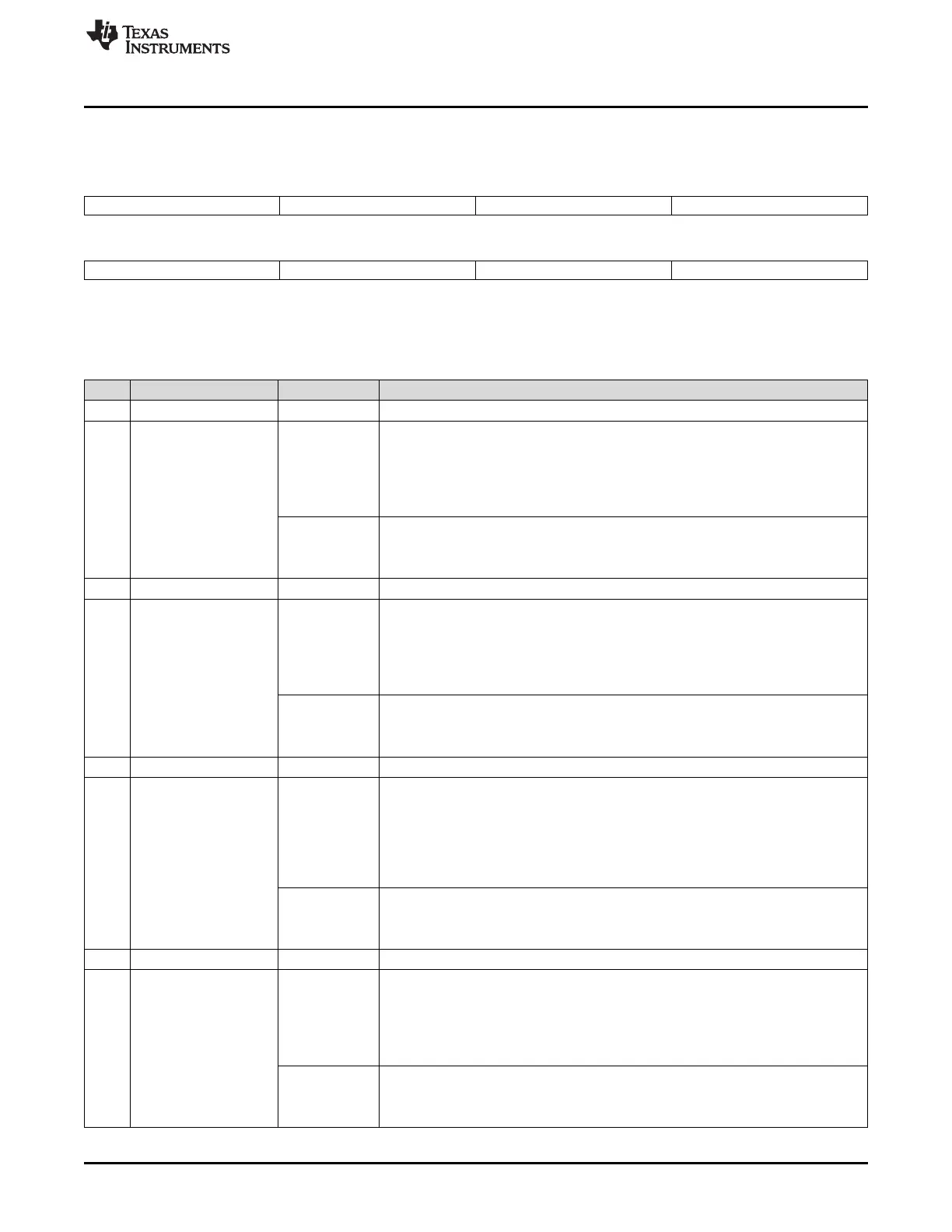

Figure 3-6. SCM Control Register (SCMCNTRL) [offset = 04h]

31 28 27 24 23 20 19 16

Reserved PAR DIAG EN Reserved GLOBAL_ERROR_CLR

R-0 R/WP-5h R-0 R/WP-5h

15 12 11 8 7 4 3 0

Reserved DTC_SOFT_RESET Reserved TO_CLEAR

R-0 R/WP-5h R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after synchronous reset on system reset

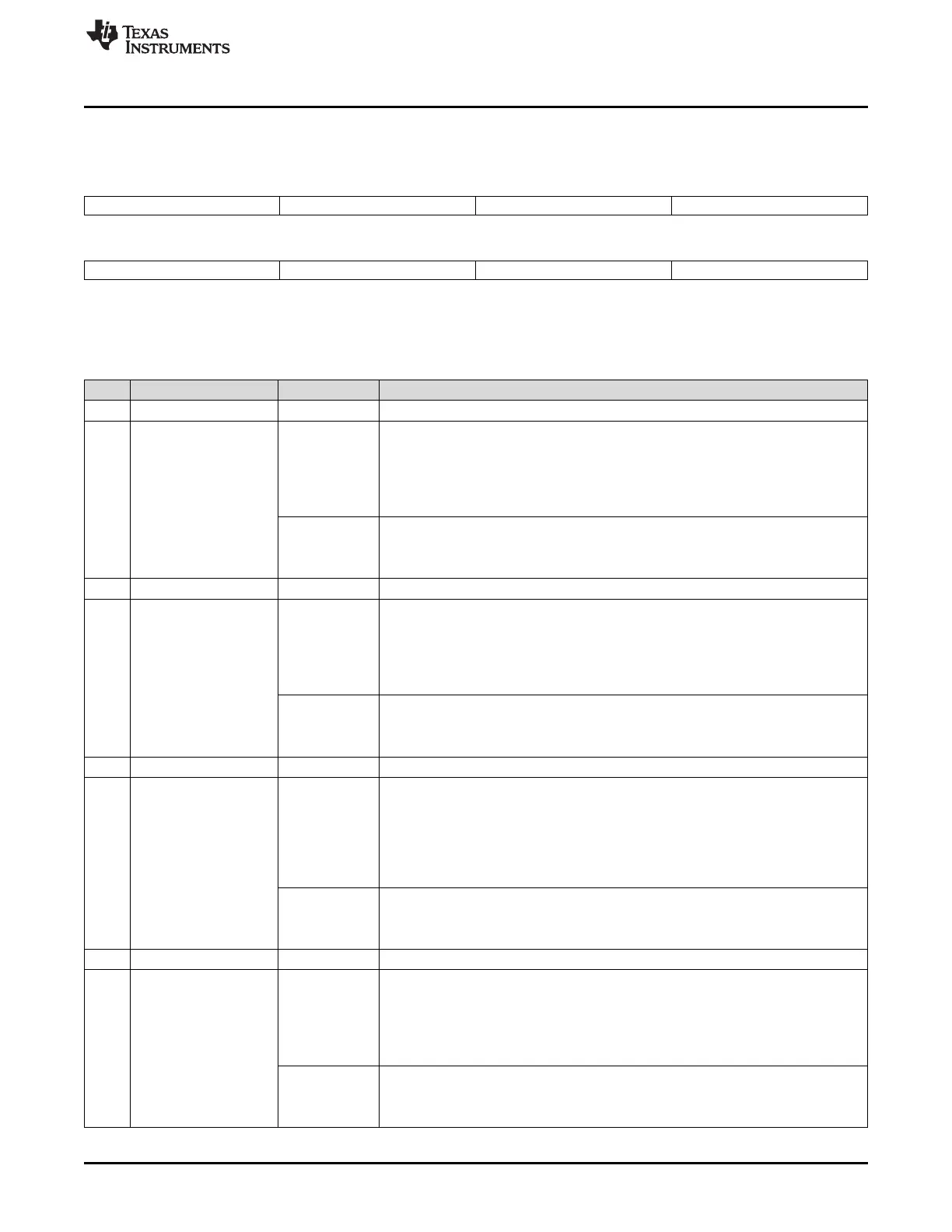

Table 3-3. SCM Control Register (SCMCNTRL) Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reserved. Reads return 0.

27-24 PAR DIAG EN Sticky key write values of Ah. Writing Ah sends out an active-high “pulse” to the SCR

and resets the key back to 5h.

Read:

5h Sticky key.

All other values Reserved

Write in Privilege:

Ah Parity diagnostic enable.

All other values Reserved

23-20 Reserved 0 Reserved. Reads return 0.

19-16 GLOBAL_ERROR_CLR Clear global error in interconnect. Writing Ah sends out a clear pulse to the SCR and

resets the key back to 5h.

Read:

5h Sticky key.

All other values Reserved

Write in Privilege:

Ah Enable global error clear.

All other values Reserved

15-12 Reserved 0 Reserved. Reads return 0.

11-8 DTC_SOFT_RESET Diagnostic self-test error enable. Writing Ah forces the SCM to initiate self-test

sequence. The hardware will reset the key back to 0x5 whenever self-test is

completed.

Read:

5h Sticky key.

All other values Reserved

Write in Privilege:

Ah Enable sequence to start interconnect self-test.

All other values Reserved

7-4 Reserved 0 Reserved. Reads return 0.

3-0 TO_CLEAR Clear real time counters inside SCR. Writing Ah sends out a clear pulse to the SCR

and resets the key back to 5h.

Read:

5h Sticky key.

All other values Reserved

Write in Privilege:

Ah Enable global error clear.

All other values Reserved

Loading...

Loading...