N

Y

Y

Y

N

Y

Y

N

Y

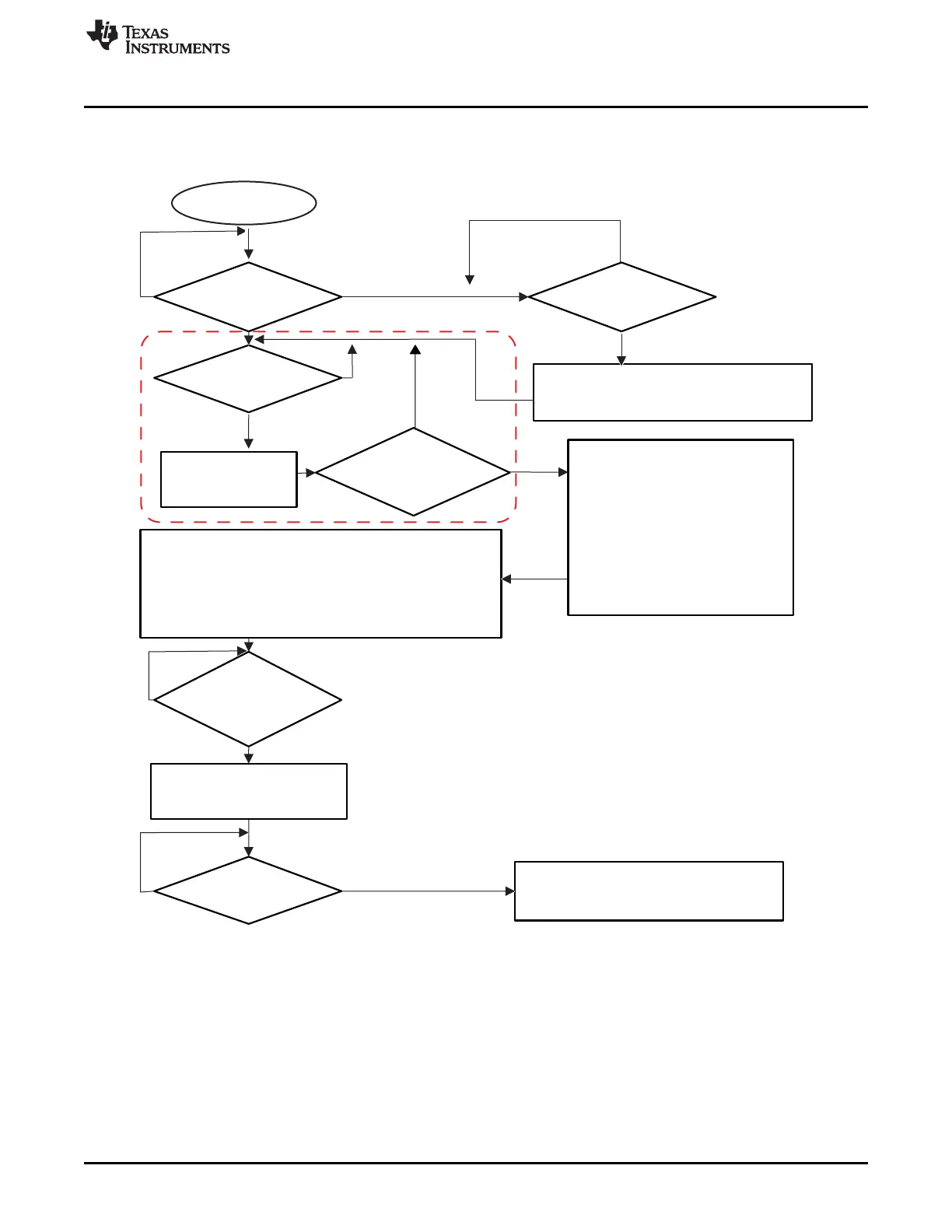

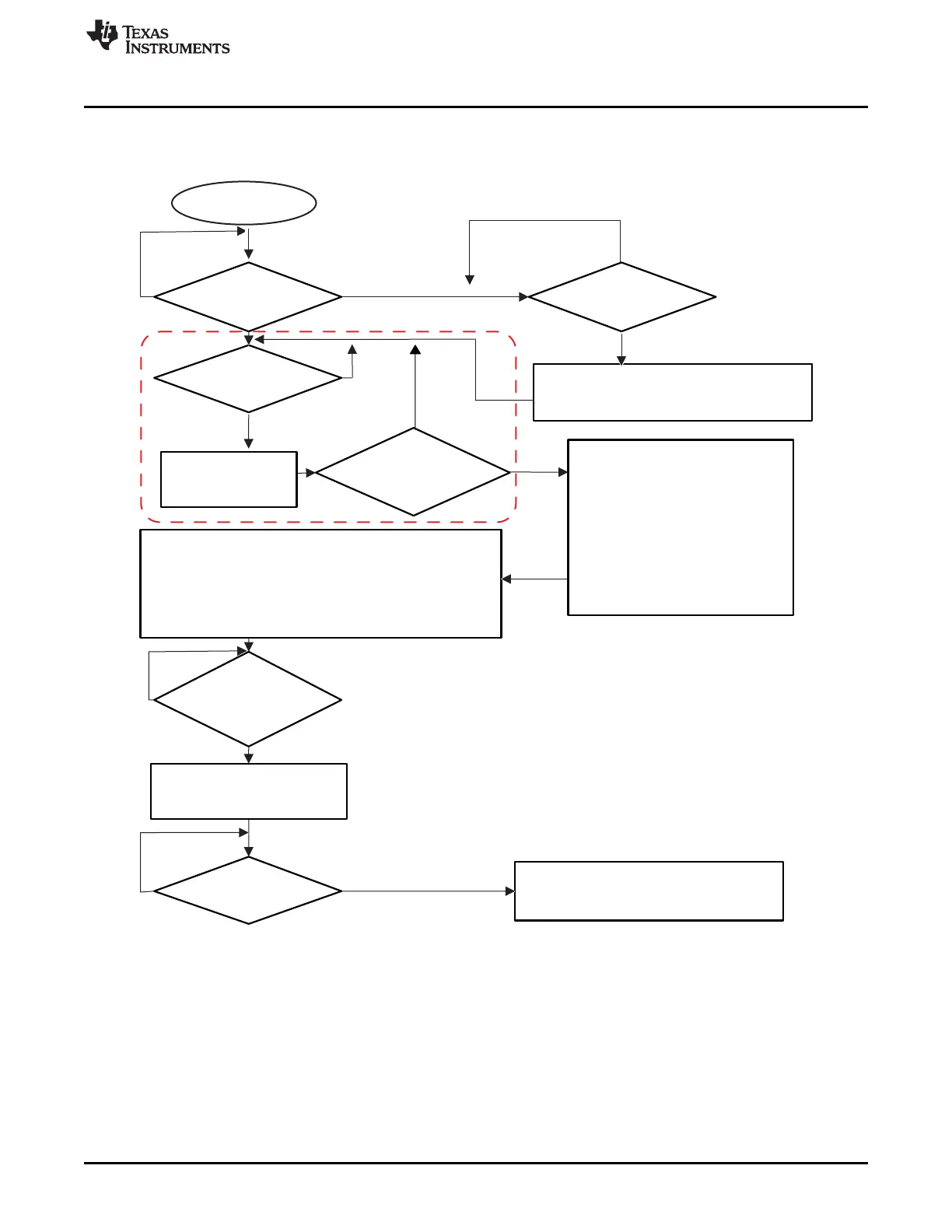

Read Self test status registers.

Retrieve MUT state if required.

Self test execution starts MUT

in safe mode

MUT idle/safe

acknowledge

1) For the logic under test, Save any Critical data/states

if required (context switch)

2) Configure the Segment/core/IP under test to be in

Idle/Safe mode (ex: the CPU in WFI mode)

3) Program STC enable

(MUT)

Program Core_SEL

for Segment0

Read back CORE_SEL.

Is the value the same?

Configure the STC run:

-STCCLKDIV registers for clock

division ratio of the source clock

for each segment

-Number of intervals for the run

and interval start type (restart,

continue from previous interval,

preload)

-Program the time out counter

Is ST_ACTIVE Key

Active?

Program SYS GHVSRC to select PLL and

program CLKCNTL registers

Self-test Done?

Is SYS_NRST = 1

SYSTEM RESET

Is PLL_LOCK = 1?

N

N

N

Loading...

Loading...