Address Decode

Peripheral bus

Register A

OFF

ON

Program RAM

internal multi-

N2HET sync

Slave

Master

HETGCR.16

HETGCR.0

32 ALU

Compare

To VIM

HETOFF2.7:0

HETOFF1.7:0

HETDOUT.31:0

HETDSET.31:0

Register R

Register B

HETDCLR.31:0

HETFLG. 31:0

HETDIN.31:0

Priority 1

Priority 2

To VIM

32

HETDIR.31:0

Rotate/

Shift by N

HETADDR.8:0

HETPRY.31:0

HR block

HET[31:0]

Control RAM Data RAM

Ignore Suspend

HETGCR.17

Stop

Shadow Registers

Shadow Registers

High Resolution

prescaler

HETPFR.5:0

Loop resolution

prescaler

HETPFR.10:8

Register S

Register T

HR clock

(to IO PIN

CONTROL)

HR clock

CURRENT INSTRUCTION

HOST

INTERFACE

N2HET

RAM

SPECIALIZED

TIMER

MICROMACHINE

I/O

PIN

CONTROL

PROGRAM FIELD CONTROL FIELD

DATA FIELD

www.ti.com

Overview

955

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

23.1.3 Block Diagram

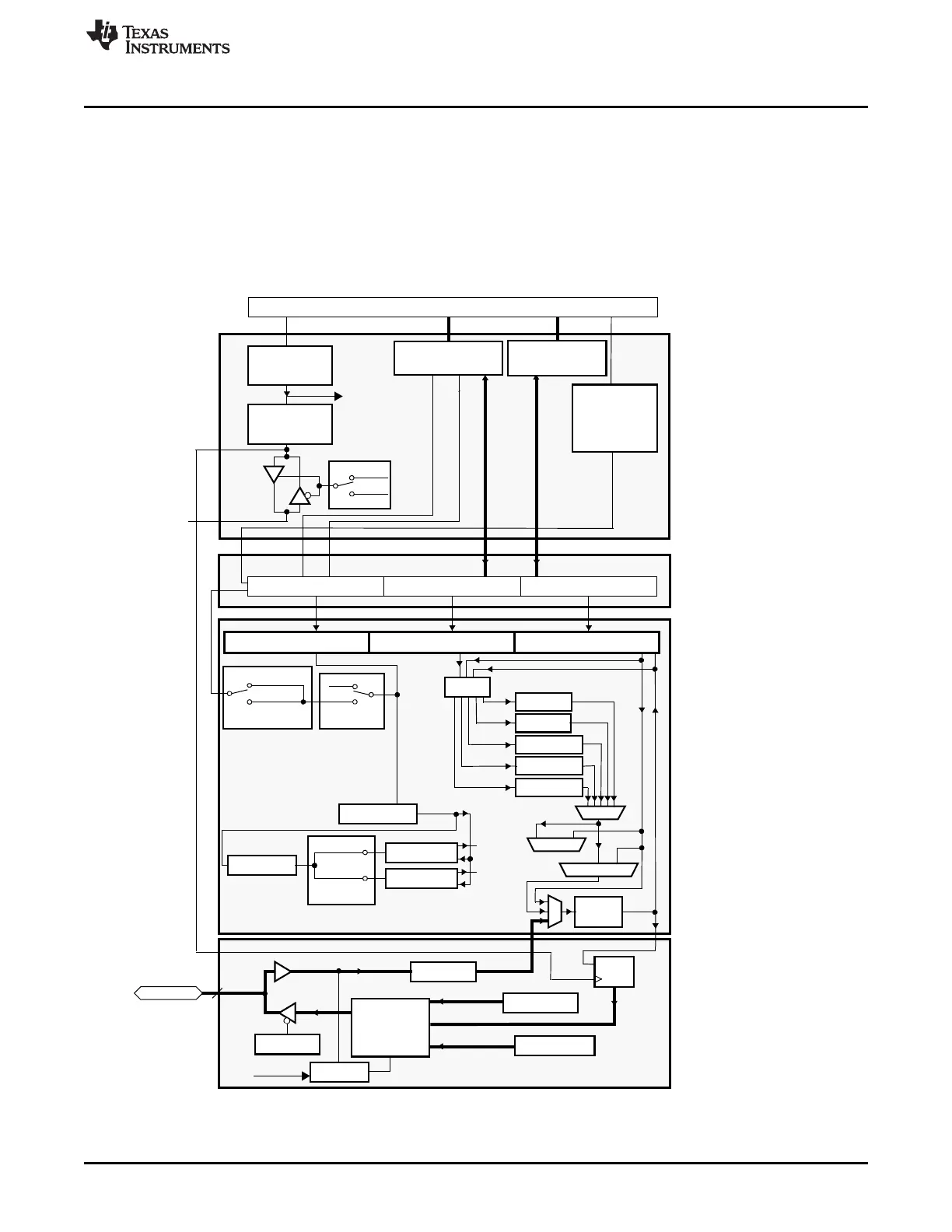

The N2HET module (see Figure 23-1) comprises four separate components:

• Host interface

• N2HET RAM

• Specialized timer micromachine

• I/O control (the N2HET is attached to an I/O port of up to 32 pins)

Figure 23-1. N2HET Block Diagram

Loading...

Loading...