Control Registers

www.ti.com

514

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

CPU Compare Module for Cortex-R5F (CCM-R5F)

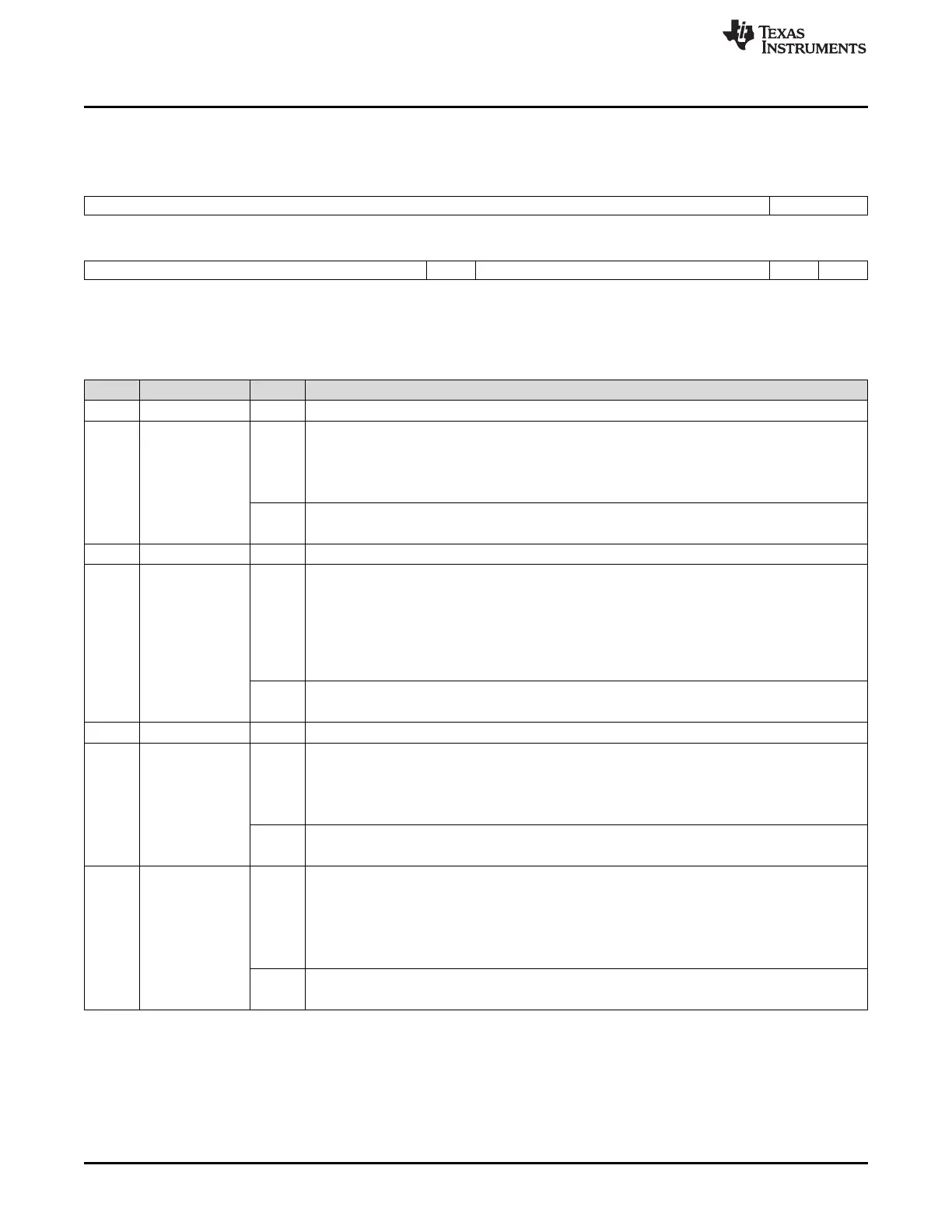

13.3.8 CCM-R5F Status Register 4 (CCMSR4)

Figure 13-10. CCM-R5F Status Register 4 (CCMSR4) (Offset = 1Ch)

31 17 16

Reserved CPME4

R-0 R/W1CP-0

15 9 8 7 2 1 0

Reserved STC4 Reserved STET4 STE4

R-0 R-0 R-0 R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 to clear in privilege mode only; -n = value after reset

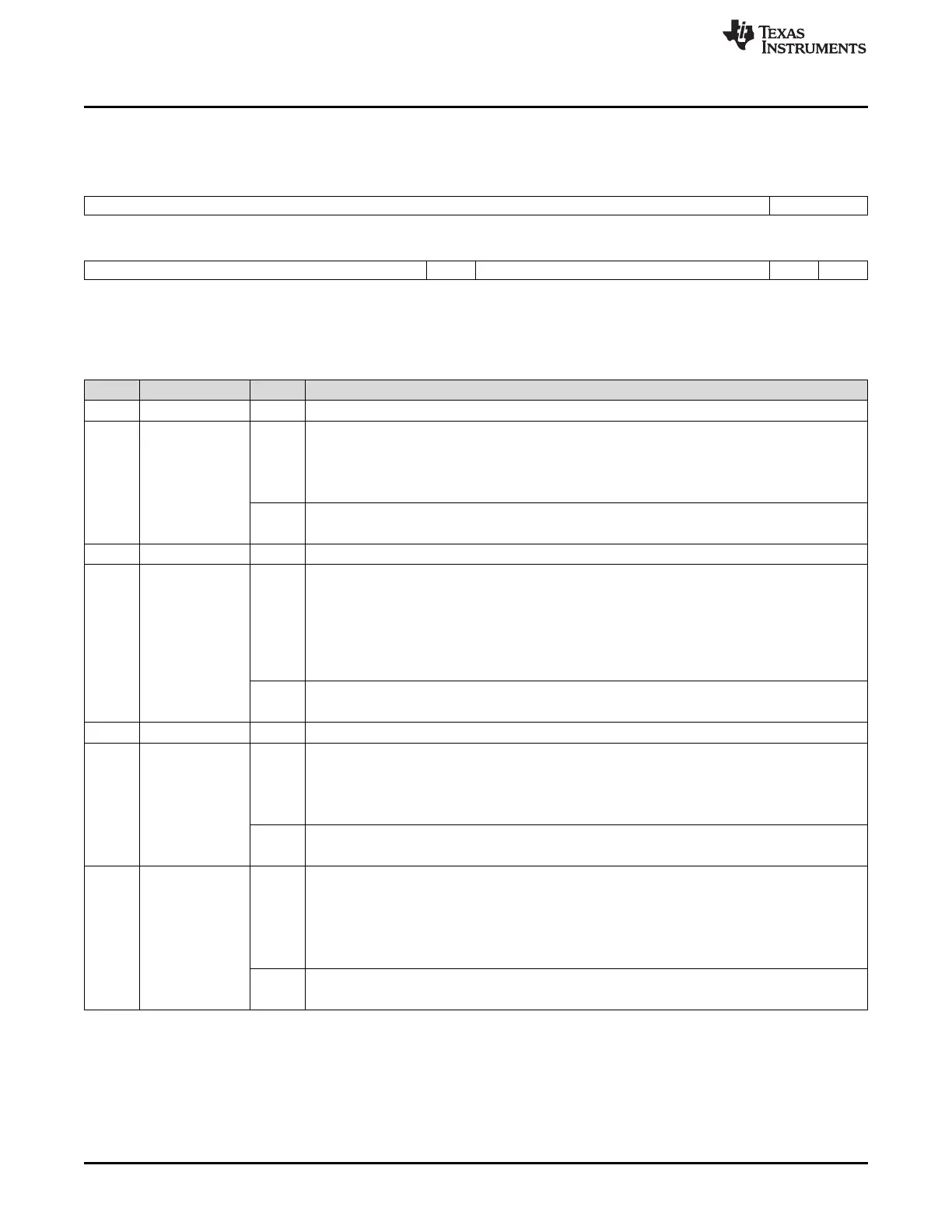

Table 13-15. CCM-R5F Status Register 4 (CCMSR4) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reads return 0. Writes have no effect.

16 CMPE4 Compare Error for Power Domain Inactivity Monitor.

Read in User and Privileged mode. Write in Privileged mode only.

0 Read: CPU signals are identical.

Write: Leaves the bit unchanged.

1 Read: CPU signal compare mismatch.

Write: Clears the bit.

15-9 Reserved Reads return 0. Writes have no effect.

8 STC4 Self-test Complete for Power Domain Inactivity Monitor.

Note: This bit is always 0 when not in self-test mode. Once set, switching from self-test mode to

other modes will clear this bit.

Read/Write in User and Privileged mode.

0 Read: Self-test on-going if self-test mode is entered.

Write: Writes have no effect.

1 Read: Self-test is complete.

Write: Writes have no effect.

7-2 Reserved Reads return 0. Writes have no effect.

1 STET4 Self-test Error Type for Power Domain Inactivity Monitor.

Read/Write in User and Privileged mode.

0 Read: Self-test failed during Compare Match Test if STE4 = 1.

Write: Writes have no effect.

1 Read: Self-test failed during Compare Mismatch Test if STE4 = 1.

Write: Writes have no effect.

0 STE4 Self-test Error for Power Domain Inactivity Monitor.

Note: This bit gets updated when the self-test is complete or an error is detected.

Read/Write in User and Privileged mode.

0 Read: Self-test passed.

Write: Writes have no effect.

1 Read: Self-test failed.

Write: Writes have no effect.

Loading...

Loading...