www.ti.com

HTU Control Registers

1151

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer Transfer Unit (HTU) Module

24.4.3 Control Packet (CP) Busy Register 0 (HTU BUSY0)

This register displays the status of individual control packets.

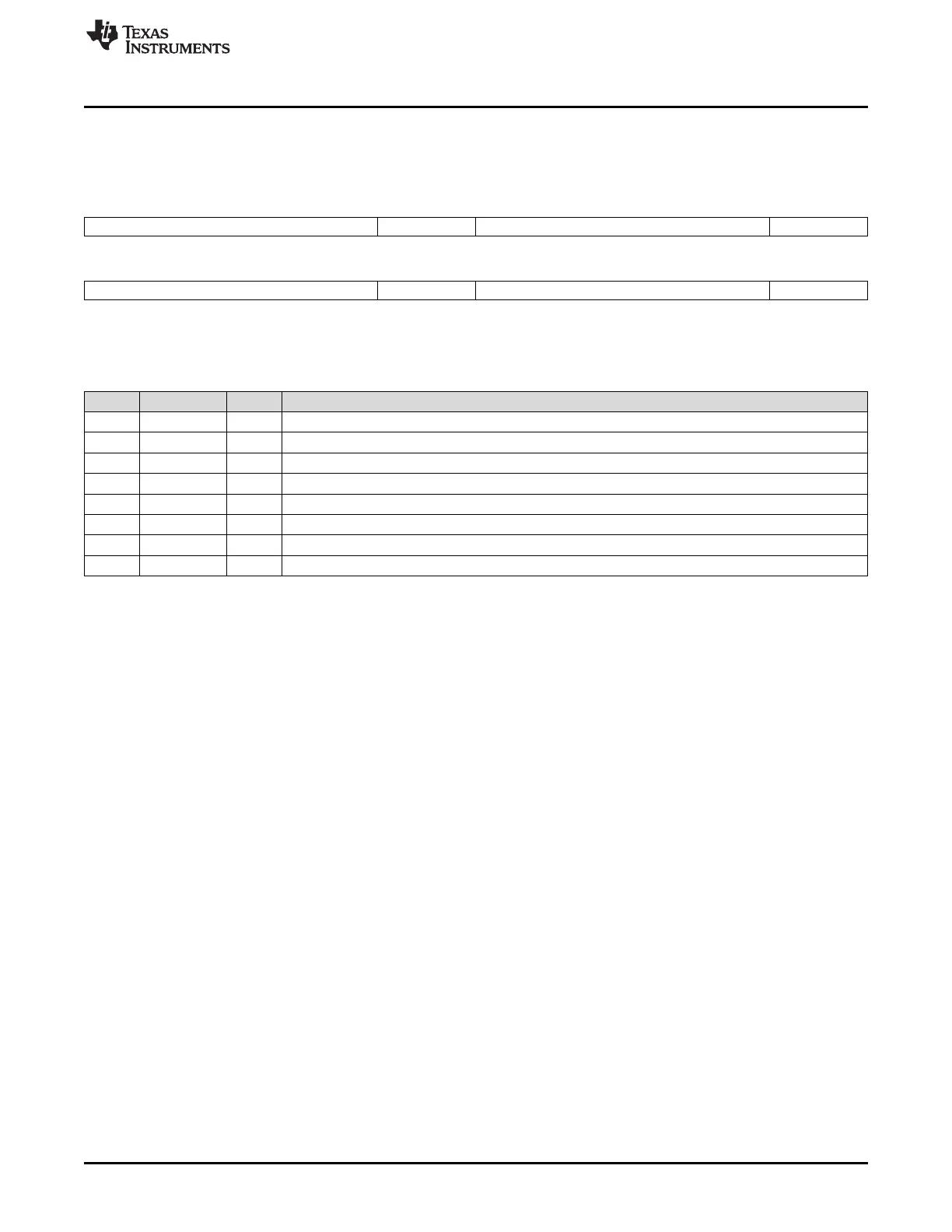

Figure 24-16. Control Packet (CP) Busy Register 0 (HTU BUSY0) [offset = 08h]

31 25 24 23 17 16

Reserved BUSY0A Reserved BUSY0B

R-0 R/W1CP-0 R-0 R/W1CP-0

15 9 8 7 1 0

Reserved BUSY1A Reserved BUSY1B

R-0 R/W1CP-0 R-0 R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 in privilege mode only to clear the bit; -n = value after reset

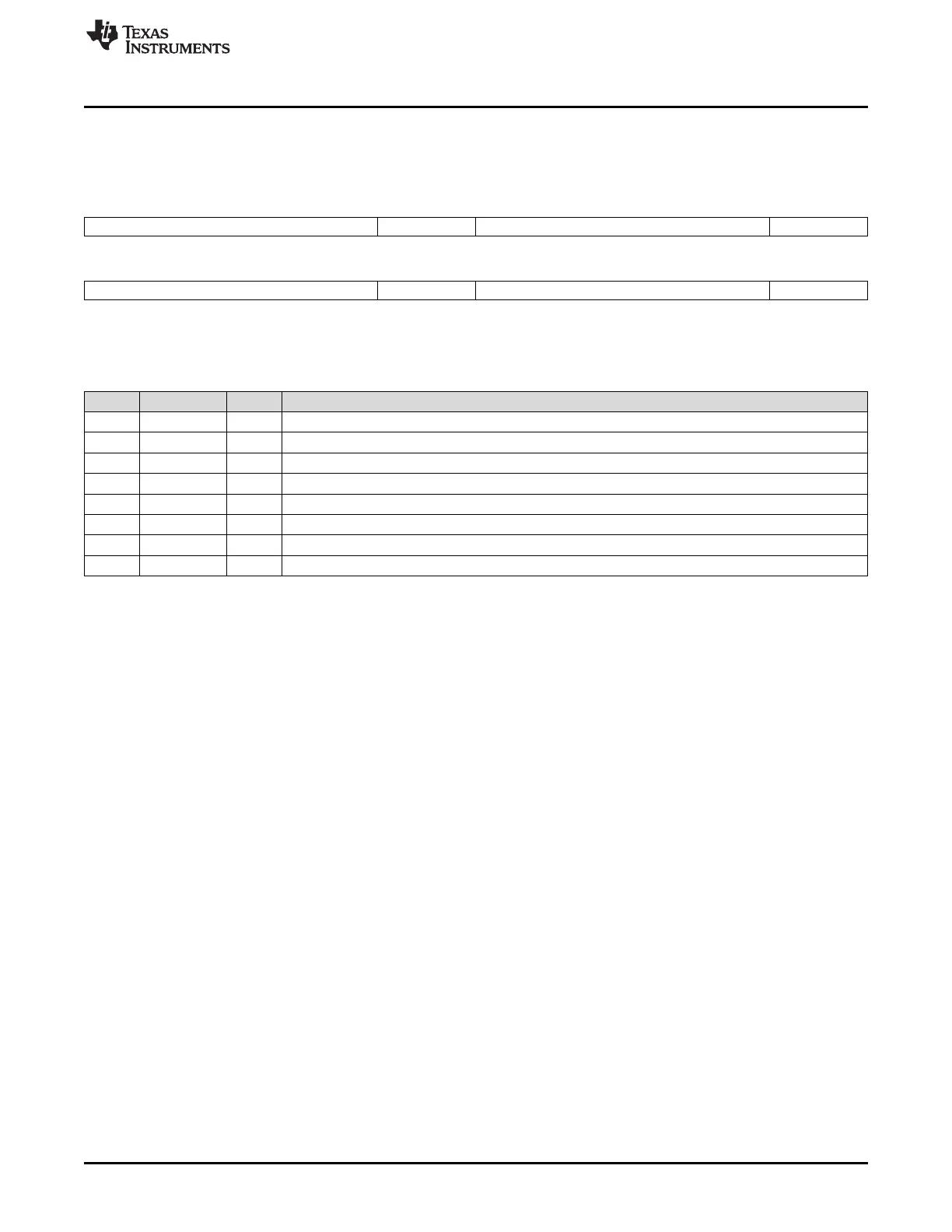

Table 24-15. Control Packet (CP) Busy Register 0 (HTU BUSY0) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads return 0. Writes have no effect.

24 BUSY0A Busy Flag for CP A of DCP 0

23-17 Reserved 0 Reads return 0. Writes have no effect.

16 BUSY0B Busy Flag for CP B of DCP 0

15-9 Reserved 0 Reads return 0. Writes have no effect.

8 BUSY1A Busy Flag for CP A of DCP 1

7-1 Reserved 0 Reads return 0. Writes have no effect.

0 BUSY1B Busy Flag for CP B of DCP 1

The bit is set when the frame on the according control packet starts (as shown in the diagram below,

there could be a delay between the request and the start of the frame).

The bit is automatically cleared at any of the following conditions:

1. At the end of a frame.

2. Writing a 1 to a BUSY bit (of DCP x) if that bit is 1. This will:

a. clear the element counter of DCP x

b. stop all new element transfers on DCP x

c. clear the busy bit

d. and disable DCP x in the CPENA register.

There is no effect, if the BUSY bit is 0.

3. At the conditions listed in Section 24.2.3.

A write access to the CPENA register can stop a control packet (CP) in single buffer mode or it can switch

to the other CP of a DCP in dual buffer mode. If stopping or switching occurs while a frame runs on the

currently active control packet, the CPU can poll the busy bit to determine when it is safe to read the

buffer.

Loading...

Loading...