www.ti.com

Double Control Packet Configuration Memory

1175

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer Transfer Unit (HTU) Module

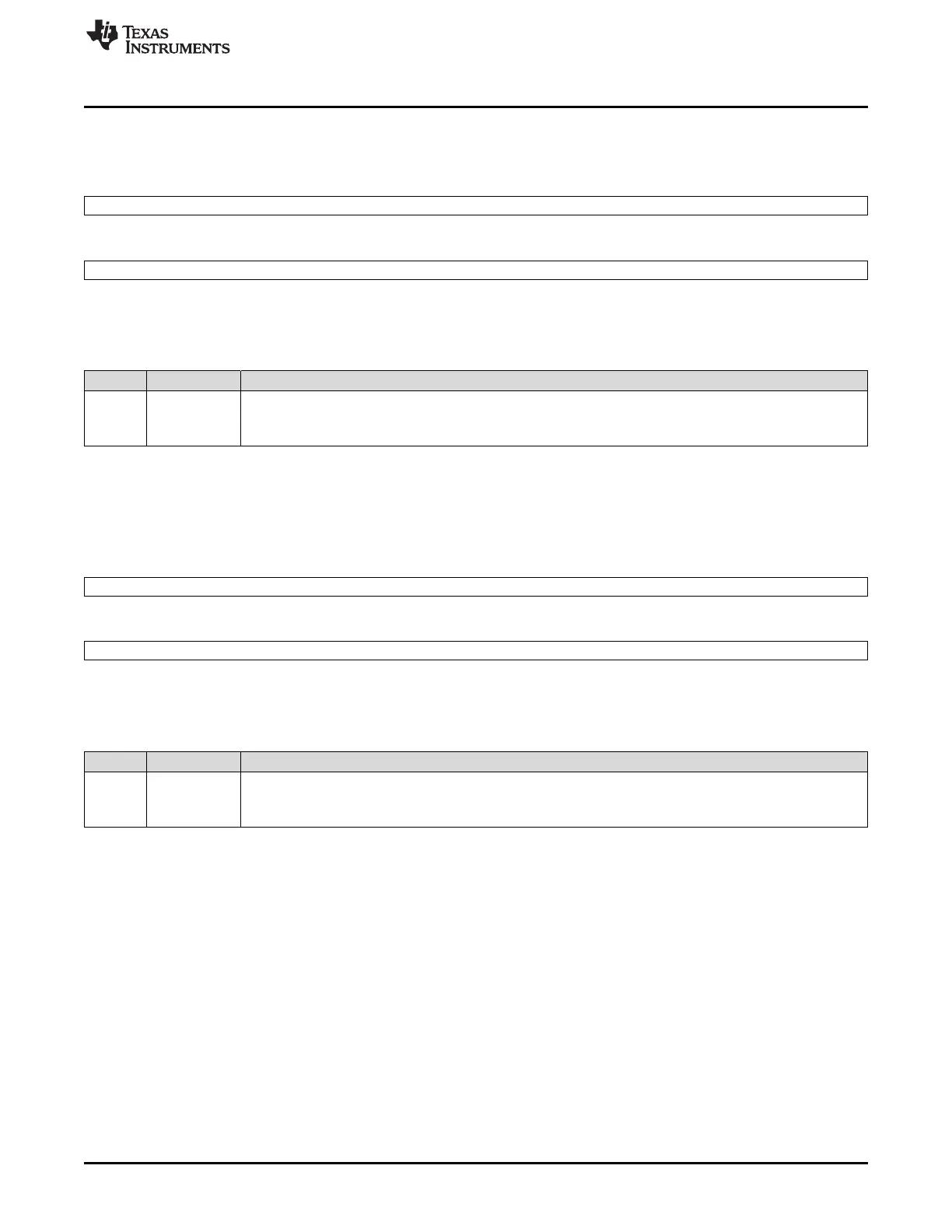

24.5.1 Initial Full Address A Register (HTU IFADDRA)

Figure 24-42. Initial Full Address A Register (HTU IFADDRA)

31 16

IFADDRA

R/WP-X

15 0

IFADDRA

R/WP-X

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -n = value after reset; X = Unknown

Table 24-43. Initial Full Address A Register (HTU IFADDRA) Field Descriptions

Bit Field Description

31-0 IFADDRA Initial Address of Buffer A in main memory.

Initial (byte) address of buffer A placed in the main memory address range. Bits 0 and 1 are ignored by the

logic, due to 32-bit alignment.

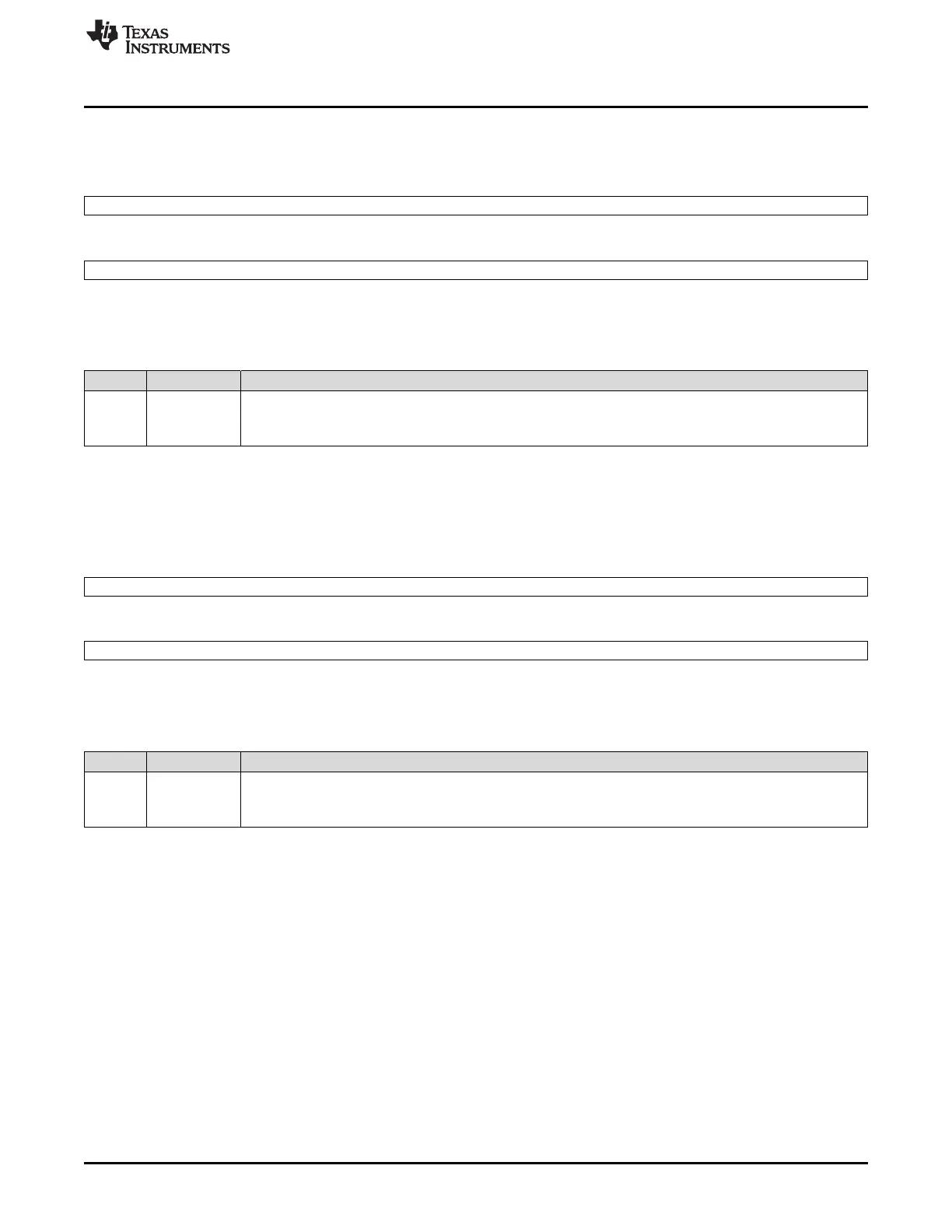

24.5.2 Initial Full Address B Register (HTU IFADDRB)

Figure 24-43. Initial Full Address B Register (HTU IFADDRB)

31 16

IFADDRB

R/WP-X

15 0

IFADDRB

R/WP-X

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -n = value after reset; X = Unknown

Table 24-44. Initial Full Address B Register (HTU IFADDRB) Field Descriptions

Bit Field Description

31-0 IFADDRB Initial Address of Buffer B in main memory.

Initial (byte) address of buffer B placed in the main memory address range. Bits 0 and 1 are ignored by the

logic, due to 32-bit alignment.

Loading...

Loading...