HWAG Registers

www.ti.com

1056

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

23.5.15 HWAG Step Width Register (HWASTWD)

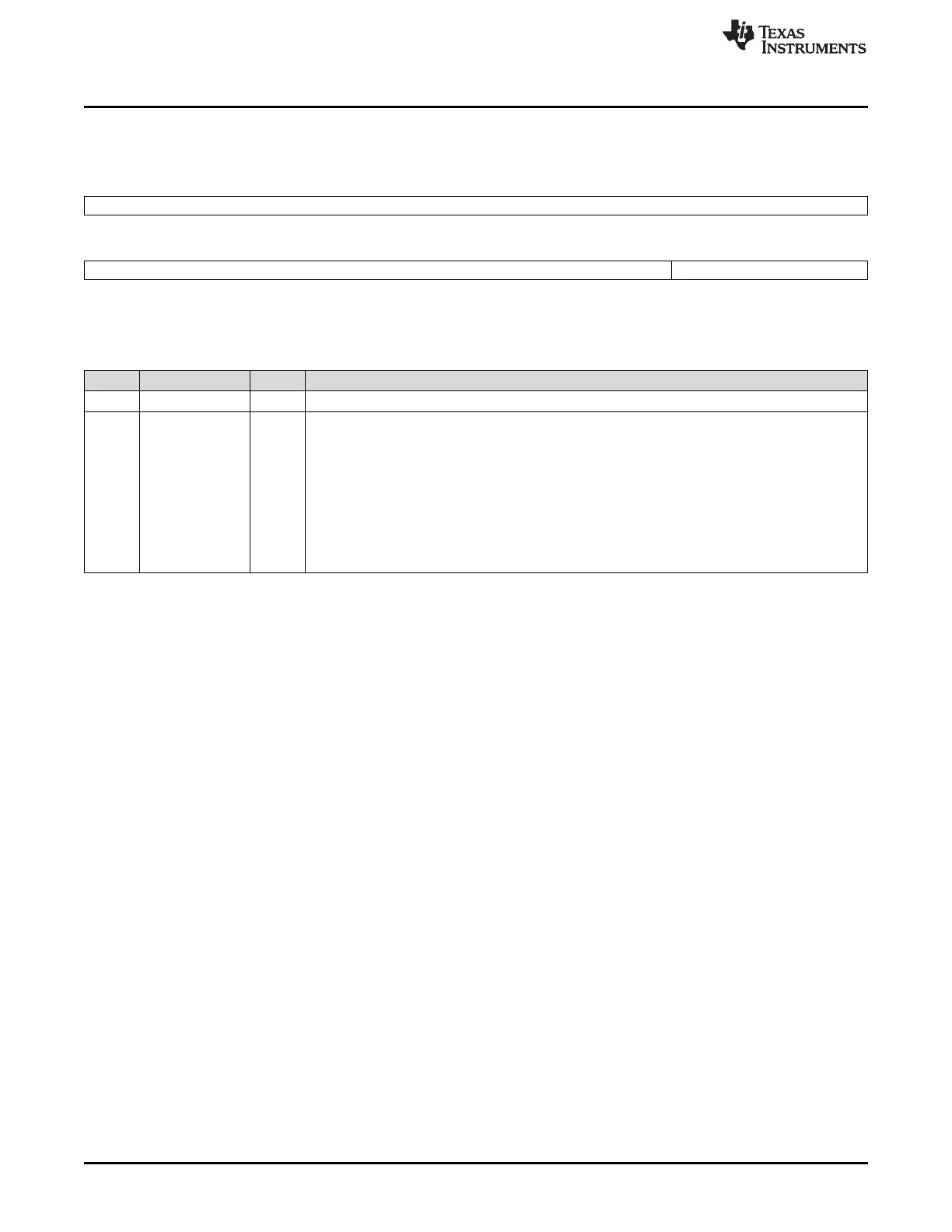

Figure 23-103. HWAG Step Width Register (HWASTWD)

31 16

Reserved

R-0

15 4 3 0

Reserved STWD

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

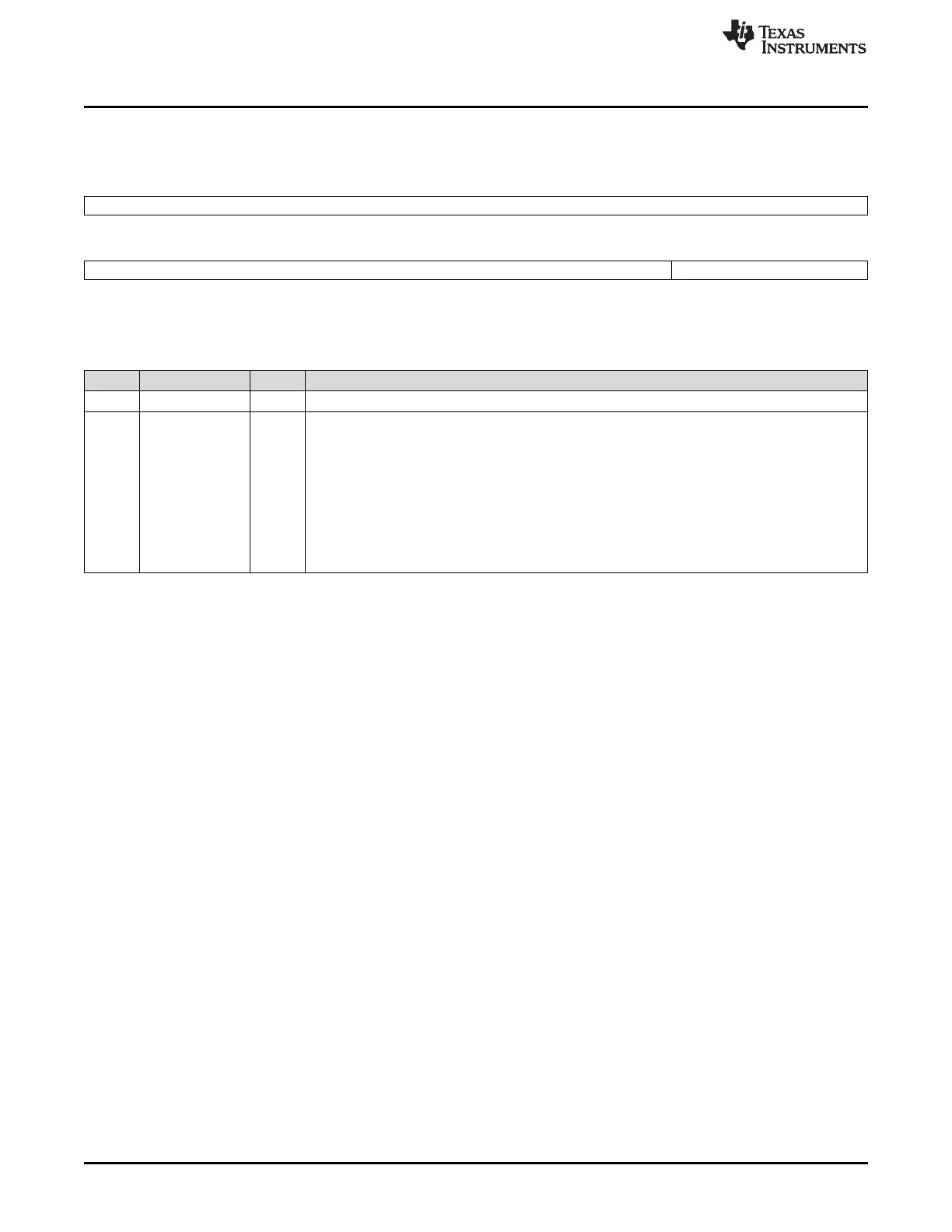

Table 23-67. HWAG Step Width Register (HWASTWD) Field Descriptions

Bit Field Value Description

31-4 Reserved Reads return 0. Writes have no effect.

3-0 STWD

Step Width. Sets the step width for the tick generation, dividing the period into K steps. (131072,

65536, ..., 8, 4). The step count is decoded from the three LSBs using the following encoding:

0h 4 ticks per period

1h 8 ticks per period

2h 16 ticks per period

: :

Eh 65536 ticks per period

Fh 131072 ticks per period

Loading...

Loading...