www.ti.com

Control and Status Registers

395

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Level 2 RAM (L2RAMW) Module

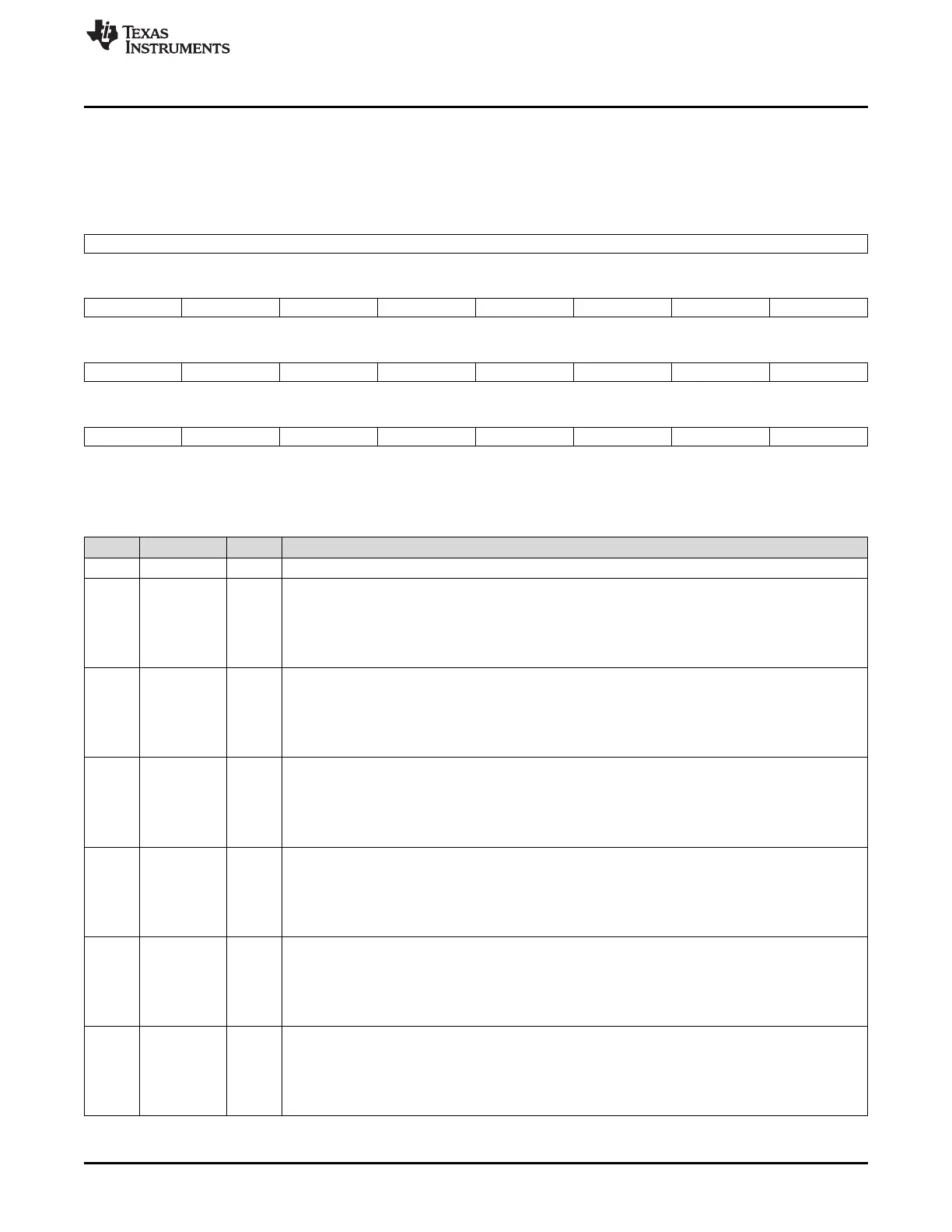

8.3.2 L2RAMW Error Status Register (RAMERRSTATUS)

The RAMERRSTATUS register, shown in Figure 8-3 and described in Table 8-4, indicates the status of

the various error conditions monitored by the L2RAMW Module.

Figure 8-3. L2RAMW Module Error Status Register (RAMERRSTATUS) (offset = 10h)

31 24

Reserved

R-0

23 22 21 20 19 18 17 16

Reserved DRDE DRSE DWDE DWSE MSSM MSRA MSACP

R-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

15 14 13 12 11 10 9 8

CPEOI Reserved MIE MMDE WEMDE REMDE MME PACE

R/W1CP-0 R-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

7 6 5 4 3 2 1 0

RMWDE Reserved CPUWDE ADDE WEME ADE REME CPUWE

R/W1CP-0 R-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Privilege Write 1 to Clear; -n = value after reset

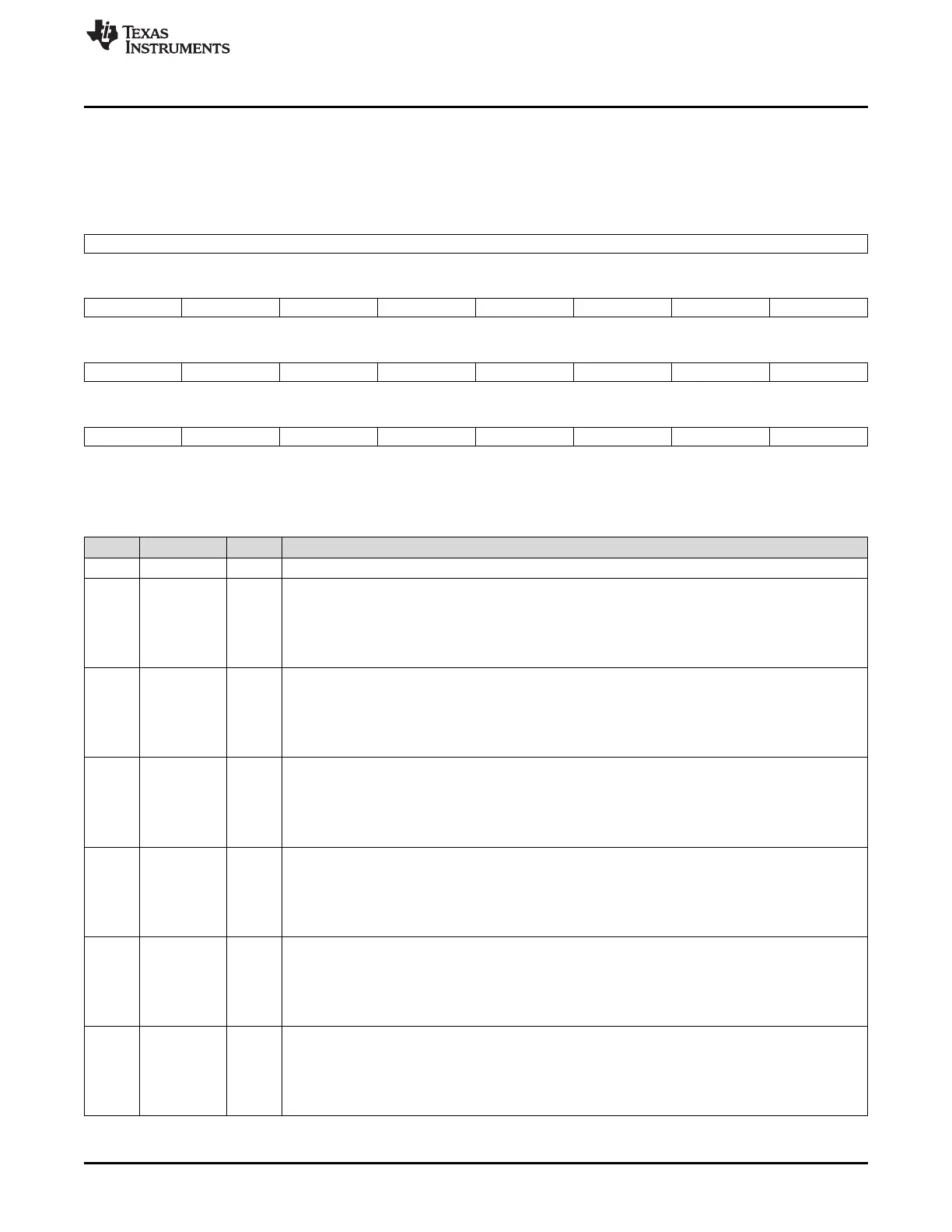

Table 8-4. L2RAMW Module Error Status Register (RAMERRSTATUS) Field Descriptions

Bit Field Value Description

31-23 Reserved 0 Reads return 0. Writes have no effect.

22 DRDE Diagnostic Read Double-bit Error. This bit indicates that a double-bit error has occurred during

diagnostic of the L2RAMW SECDED logic that is used to handle read of read-modify write operations.

This bit must be cleared by writing a 1 to it before any new error can be generated.

0 A double-bit error did not occur during diagnostic.

1 A double-bit error occurred during diagnostic.

21 DRSE Diagnostic Read Single-bit Error. This bit indicates that a single-bit error has occurred during diagnostic

of the L2RAMW SECDED logic that is used to handle read of read-modify write operations. This bit

must be cleared by writing a 1 to it before any new error can be generated.

0 A single-bit error did not occur during diagnostic.

1 A single-bit error occurred during diagnostic.

20 DWDE Diagnostic Write Double-bit Error. This bit indicates that a double-bit error has occurred during

diagnostic of the L2RAMW SECDED logic that handles write operations. This bit must be cleared by

writing a 1 to it before any new error can be generated.

0 A double-bit error did not occur during diagnostic.

1 A double-bit error occurred during diagnostic.

19 DWSE Diagnostic Write Single-bit Error. This bit indicates that a single-bit error has occurred during diagnostic

of the L2RAMW SECDED logic that handles write operations. This bit must be cleared by writing a 1 to

it before any new error can be generated.

0 A single-bit error did not occur during diagnostic.

1 A single-bit error occurred during diagnostic.

18 MSSM Memory Scrubbing write back SECDED Malfunction. This indicates that a SECDED malfunction

occurred during memory scrubbing write back. This bit must be cleared by writing a 1 to it before any

new error can be generated.

0 A SECDED malfunction did not occur during scrubbing write back.

1 A SECDED malfunction occurred during scrubbing write back.

17 MSRA Memory Scrubbing write back Redundant Address decode error. This bit indicates that a redundant

address decode error occurred during memory scrubbing write back. This bit must be cleared by writing

a 1 to it before any new error can be generated.

0 An address decode error did not occur during scrubbing write back.

1 An address decode error occurred during scrubbing write back.

Loading...

Loading...