DCAN Control Registers

www.ti.com

1484

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.26 IF1/IF2 Message Control Registers (DCAN IF1MCTL, DCAN IF2MCTL)

The bits of the IF1/IF2 Message Control Registers mirror the message control bits of a message object.

The function of the relevant message objects bits is described in Section 27.5.1.

NOTE: While Busy bit of IF1/IF2 Command Register is one, IF1/IF2 Register Set is write protected.

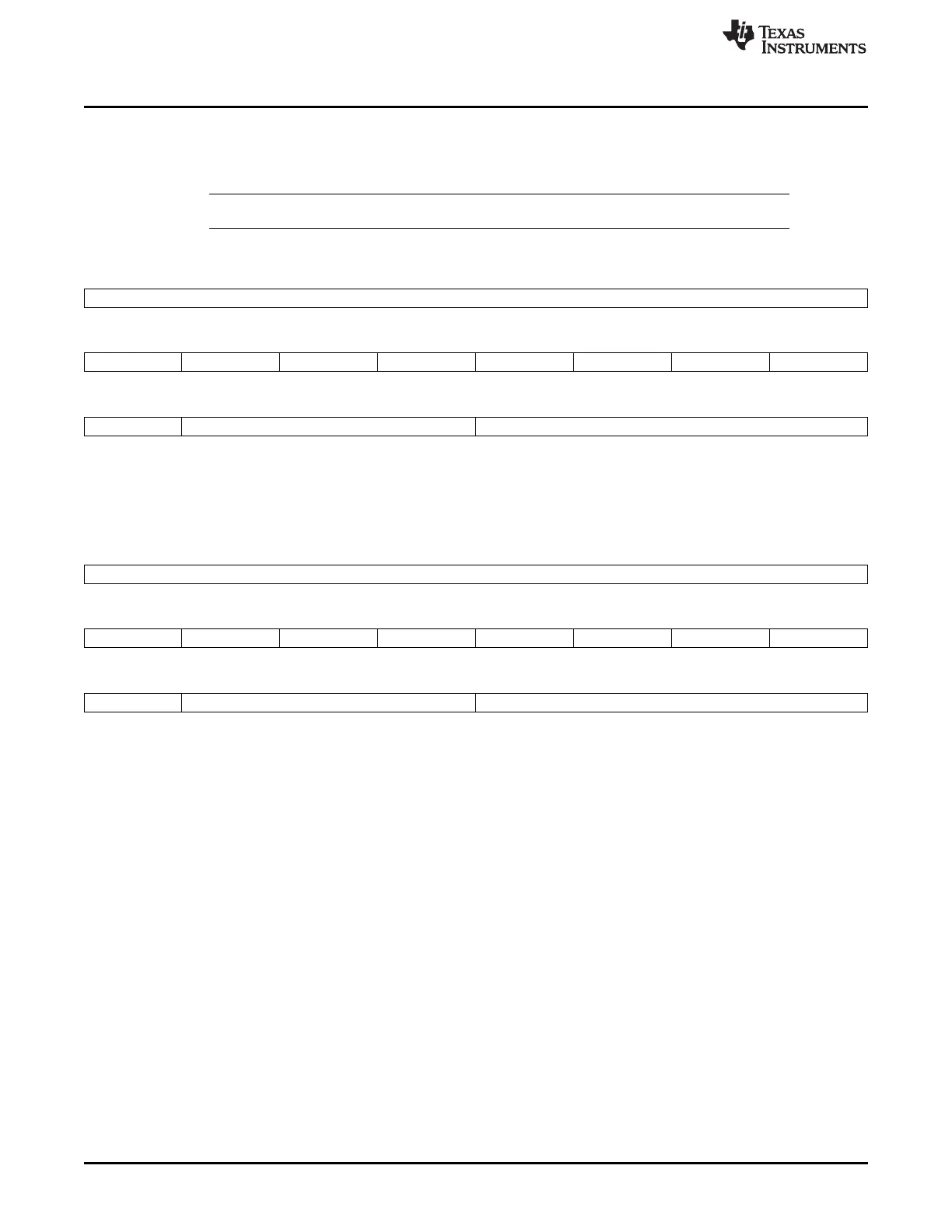

Figure 27-63. IF1 Message Control Register (DCAN IF1MCTL) [offset = 10Ch]

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

NewDat MsgLst IntPnd UMask TxIE RxIE RmtEn TxRqst

R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0

7 6 4 3 0

EoB Reserved DLC

R/WP-0 R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read; WP = Protected Write (protected by Busy bit); -n = value after reset

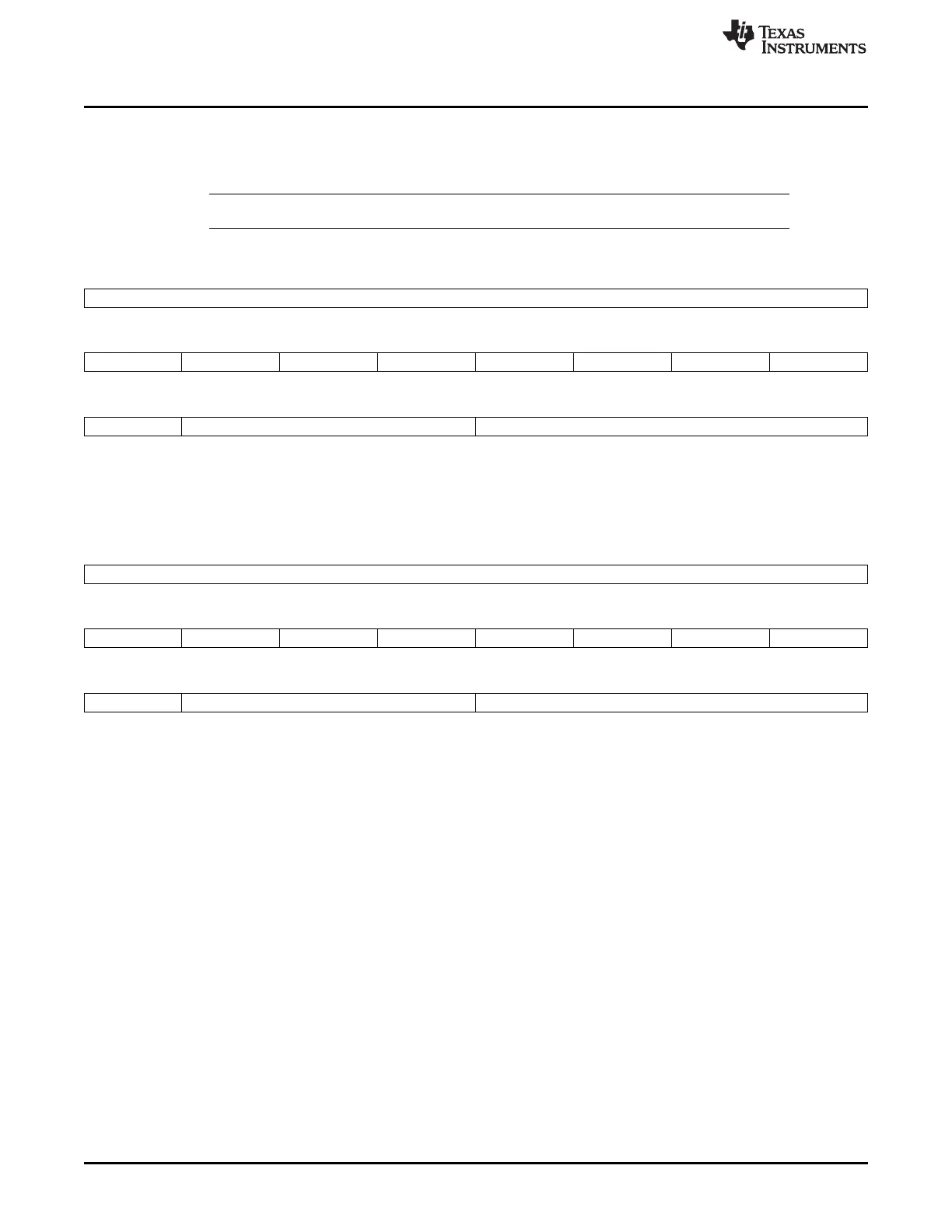

Figure 27-64. IF2 Message Control Register (DCAN IF2MCTL) [offset = 12Ch]

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

NewDat MsgLst IntPnd UMask TxIE RxIE RmtEn TxRqst

R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0

7 6 4 3 0

EoB Reserved DLC

R/WP-0 R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read; WP = Protected Write (protected by Busy bit); -n = value after reset

Loading...

Loading...