www.ti.com

Exceptions

139

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.3 Exceptions

An “Exception” is an event that makes the processor temporarily halt the normal flow of program

execution, for example, to service an interrupt from a peripheral. Before attempting to handle an

exception, the processor preserves the critical parts of the current processor state so that the original

program can resume when the handler routine has finished.

The following sections describe three exceptions – Reset, Abort and the System Software Interrupts.

For complete details on all exceptions, refer to the ARM

®

Cortex

®

-R5F Technical Reference Manual.

2.3.1 Resets

The TMS570LC43x microcontroller can be reset by either of the conditions described in Table 2-8. Each

reset condition is indicated in the System Exception Status Register (SYSESR).

The device nRST terminal is an I/O. It can be driven low by an external circuit to force a warm reset on the

microcontroller. This terminal will be driven low as an output for a minimum of 32 peripheral clock (VCLK)

cycles for any device system reset condition. As a result the EXTRST bit in the SYSESR register,

SYSESR[3], gets set for all reset conditions listed in Table 2-8. The nRST is driven low as an output for a

longer duration during device power-up or whenever the power-on reset (nPORRST) is driven low

externally. Refer the device data manual for the electrical and timing specifications for the nRST.

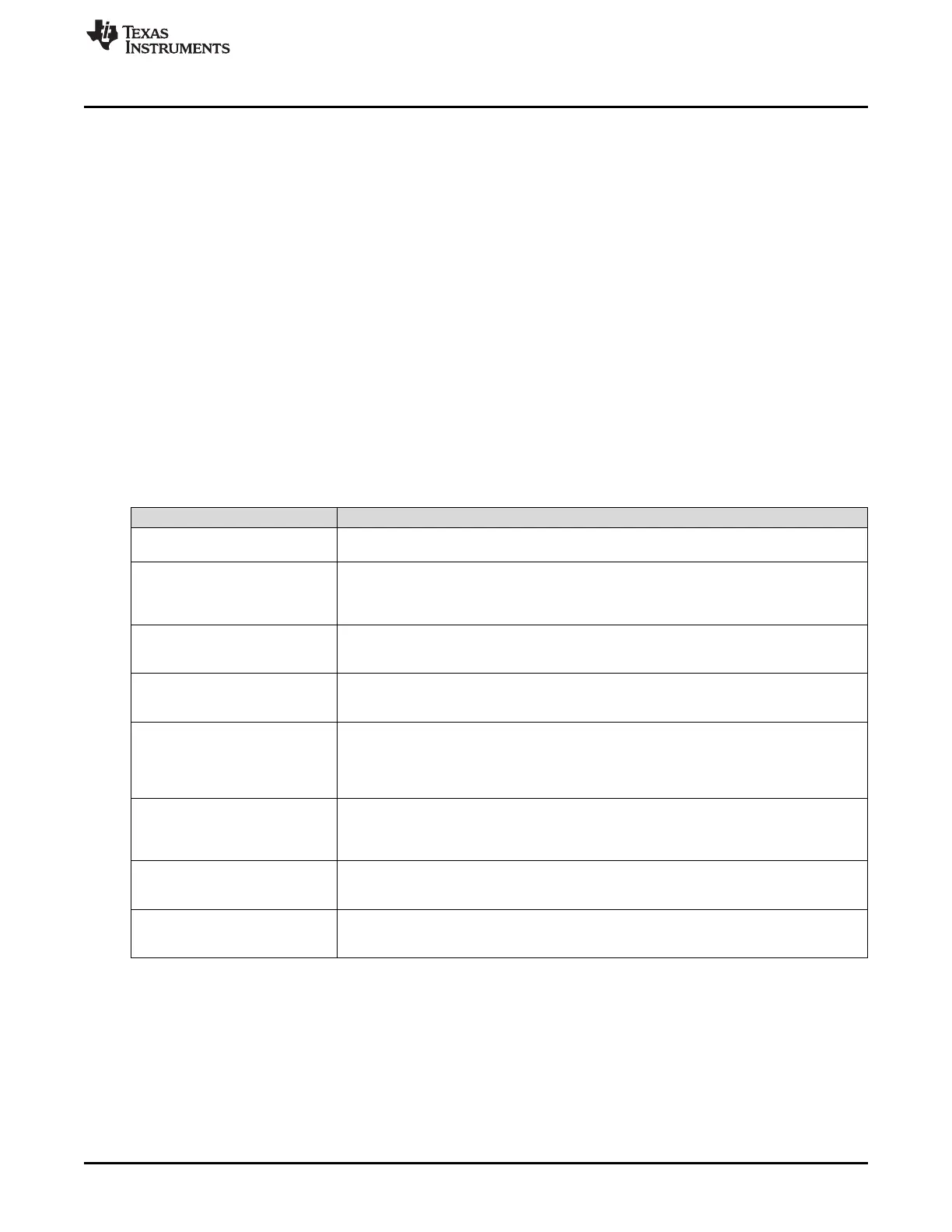

Table 2-8. Causes of Resets

Condition Description

Driving nPORRST pin low

externally

Cold reset, or power-on reset. This reset signal is typically driven by an external voltage

supervisor. This reset is flagged by the PORST bit in the SYSESR register, SYSESR[15].

Voltage Monitor reset The microcontroller has an embedded voltage monitor that generates a power-on reset when

the core voltage gets out of a valid range, or when the I/O voltage falls below a threshold.

This reset is also flagged by the PORST bit in the SYSESR register, SYSESR[15].

Note: The voltage monitor is not an alternative for an external voltage supervisor.

Driving nRST pin low externally Warm reset. This reset input is typically used in a system with multiple ICs and which requires

that the microcontroller also gets reset whenever the other IC detects a fault condition. This

reset is flagged by the EXTRST bit in the SYSESR, register SYSESR[3].

Oscillator failure This reset is generated by the system module when the clock monitor detects an oscillator fail

condition. Whether or not a reset is generated is also dictated by a register in the system

module. This reset is flagged by the OSCRST bit in the SYSESR register, SYSESR[14].

Software reset This reset is generated by the application software writing a 1 to bit 15 of System Exception

Control Register (SYSECR) or a 0 to bit 14 of SYSECR. It is typically used by a bootloader

type of code that uses a software reset to allow the code execution to branch to the

application code once it is programmed into the program memory. This reset is flagged by the

SWRST bit in the SYSESR register, SYSESR[4].

CPU reset This reset is generated by the CPU self-test controller (LBIST) or by changing the memory

protection (MMU/MPU) configuration in the CPURSTCR register or after the CPU

Interconnect Subsystem self test. This reset is flagged by the CPURST bit in the SYSESR

register, SYSESR[5].

Debug reset The ICEPICK logic implemented on the microcontroller allows a system reset to be generated

via the debug logic. This reset is flagged by the DBGRST bit in the SYSESR register,

SYSESR[13].

Watchdog reset This reset is generated by the digital windowed watchdog (DWWD) module on the

microcontroller. The DWWD can generate a reset whenever the watchdog service window is

violated. This reset is flagged by the WDRST bit in the SYSESR register, SYSESR[13].

2.3.2 Aborts

When the ARM Cortex-R5F processor's memory system cannot complete a memory access successfully,

an abort is generated. An error occurring on an instruction fetch generates a prefetch abort. Errors

occurring on data accesses generate data aborts. Aborts are also categorized as being either precise or

imprecise.

Loading...

Loading...