Memory Organization

www.ti.com

138

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

(1)

If parity protection is enabled for the peripheral SRAM modules, then the parity bits will also be initialized along with the SRAM

modules.

(2)

If ECC protection is enabled for the CPU data RAM or peripheral SRAM modules, then the auto-initialization process also

initializes the corresponding ECC space.

(3)

The level 2 SRAM range from 128kB to 512kB is divided into 6 memory regions. Each region has an associated control bit to

enable auto-initialization.

(4)

The MibSPIx modules perform an initialization of the transmit and receive RAMs as soon as the multi-buffered mode is enabled.

This is independent of whether the application has already initialized these RAMs using the auto-initialization method or not. The

MibSPIx modules need to be released from reset by writing 1 to their SPIGCR0 registers before starting auto-initialization on

their respective RAMs.

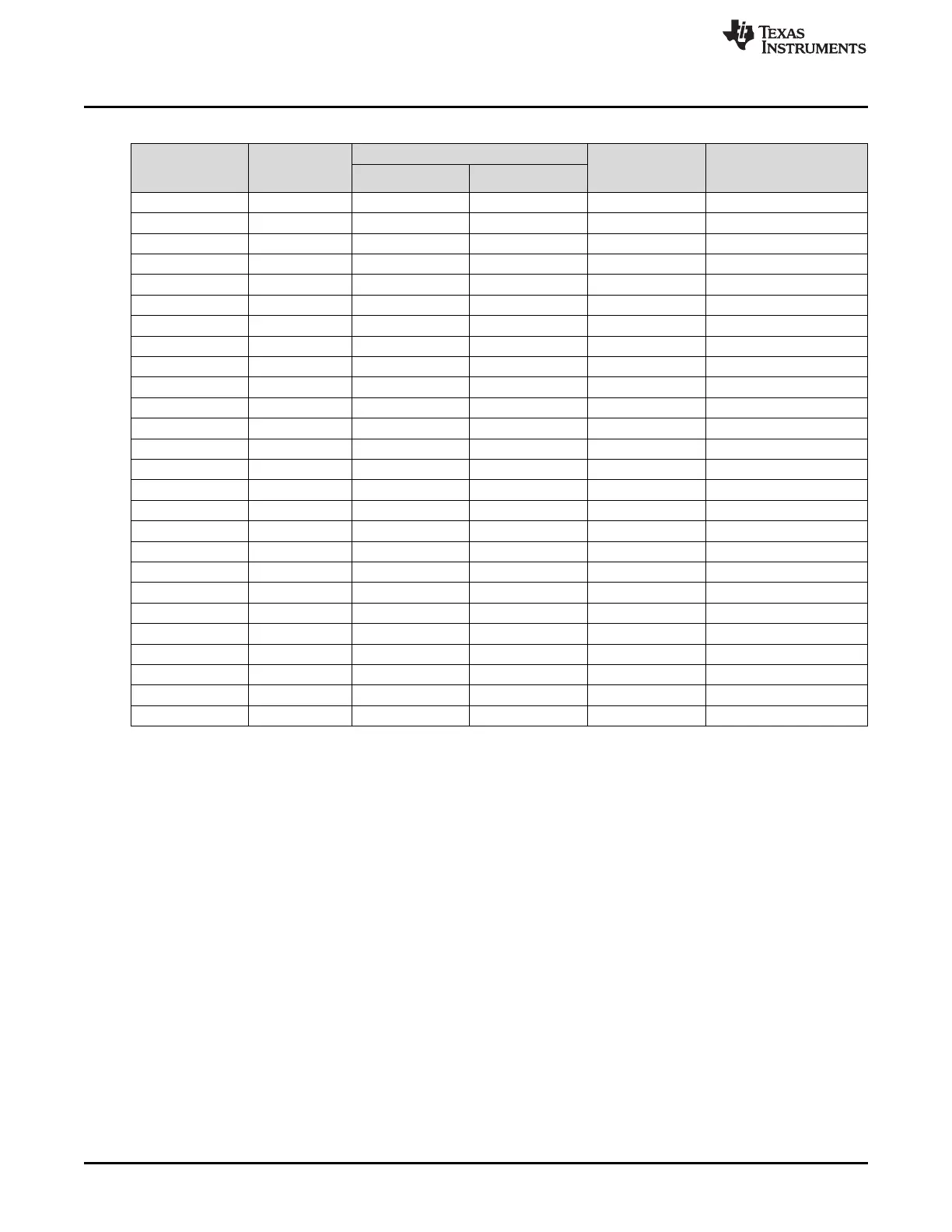

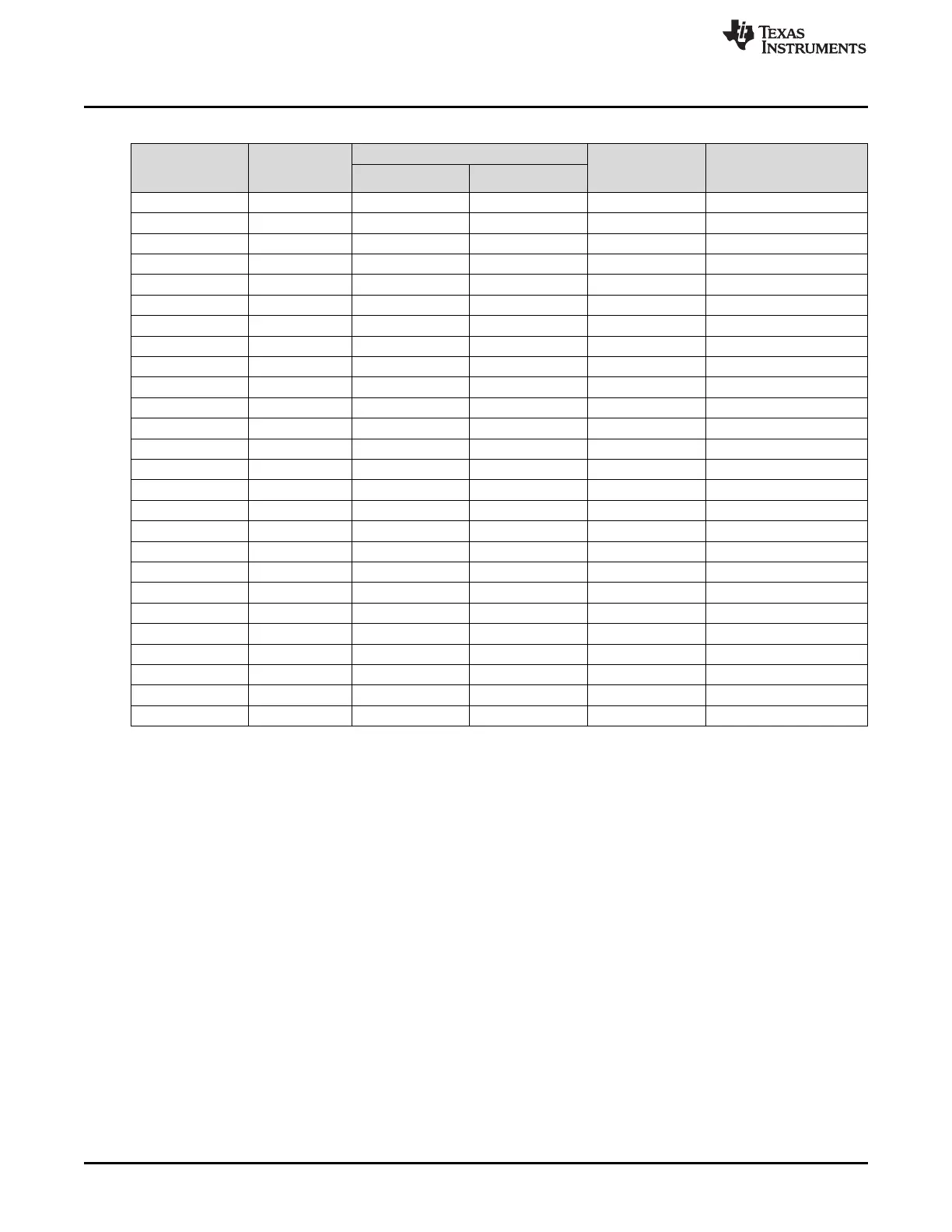

Table 2-7. Memory Initialization Select Mapping

(1)(2)

Connecting

Module

Memory

Protection

Scheme

Address Range

SYS.MSINENA

Register Bit #

L2RAMW.MEMINT_ENA

Register Bit #

(3)

Base Address Ending Address

L2 SRAM ECC 0x08000000 0x0800FFFF 0 0

L2 SRAM ECC 0x08010000 0x0801FFFF 0 1

L2 SRAM ECC 0x08020000 0x0802FFFF 0 2

L2 SRAM ECC 0x08030000 0x0803FFFF 0 3

L2 SRAM ECC 0x08040000 0x0804FFFF 0 4

L2 SRAM ECC 0x08050000 0x0805FFFF 0 5

L2 SRAM ECC 0x08060000 0x0806FFFF 0 6

L2 SRAM ECC 0x08070000 0x0807FFFF 0 7

MIBSPI5 RAM

(4)

ECC 0xFF0A0000 0xFF0BFFFF 12 n/a

MIBSPI4 RAM

(4)

ECC 0xFF060000 0xFF07FFFF 19 n/a

MIBSPI3 RAM

(4)

ECC 0xFF0C0000 0xFF0DFFFF 11 n/a

MIBSPI2 RAM

(4)

ECC 0xFF080000 0xFF09FFFF 18 n/a

MIBSPI1 RAM

(4)

ECC 0xFF0E0000 0xFF0FFFFF 7 n/a

DCAN4 RAM ECC 0xFF180000 0xFF19FFFF 20 n/a

DCAN3 RAM ECC 0xFF1A0000 0xFF1BFFFF 10 n/a

DCAN2 RAM ECC 0xFF1C0000 0xFF1DFFFF 6 n/a

DCAN1 RAM ECC 0xFF1E0000 0xFF1FFFFF 5 n/a

MIBADC2 RAM Parity 0xFF3A0000 0xFF3BFFFF 14 n/a

MIBADC1 RAM Parity 0xFF3E0000 0xFF3FFFFF 8 n/a

NHET2 RAM Parity 0xFF440000 0xFF45FFFF 15 n/a

NHET1 RAM Parity 0xFF460000 0xFF47FFFF 3 n/a

HET TU2 RAM Parity 0xFF4C0000 0xFF4DFFFF 16 n/a

HET TU1 RAM Parity 0xFF4E0000 0xFF4FFFFF 4 n/a

DMA RAM ECC 0xFFF80000 0xFFF80FFF 1 n/a

VIM RAM ECC 0xFFF82000 0xFFF82FFF 2 n/a

FlexRay TU RAM ECC 0xFF500000 0xFF51FFFF 13 n/a

Loading...

Loading...