Control Registers

www.ti.com

1556

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

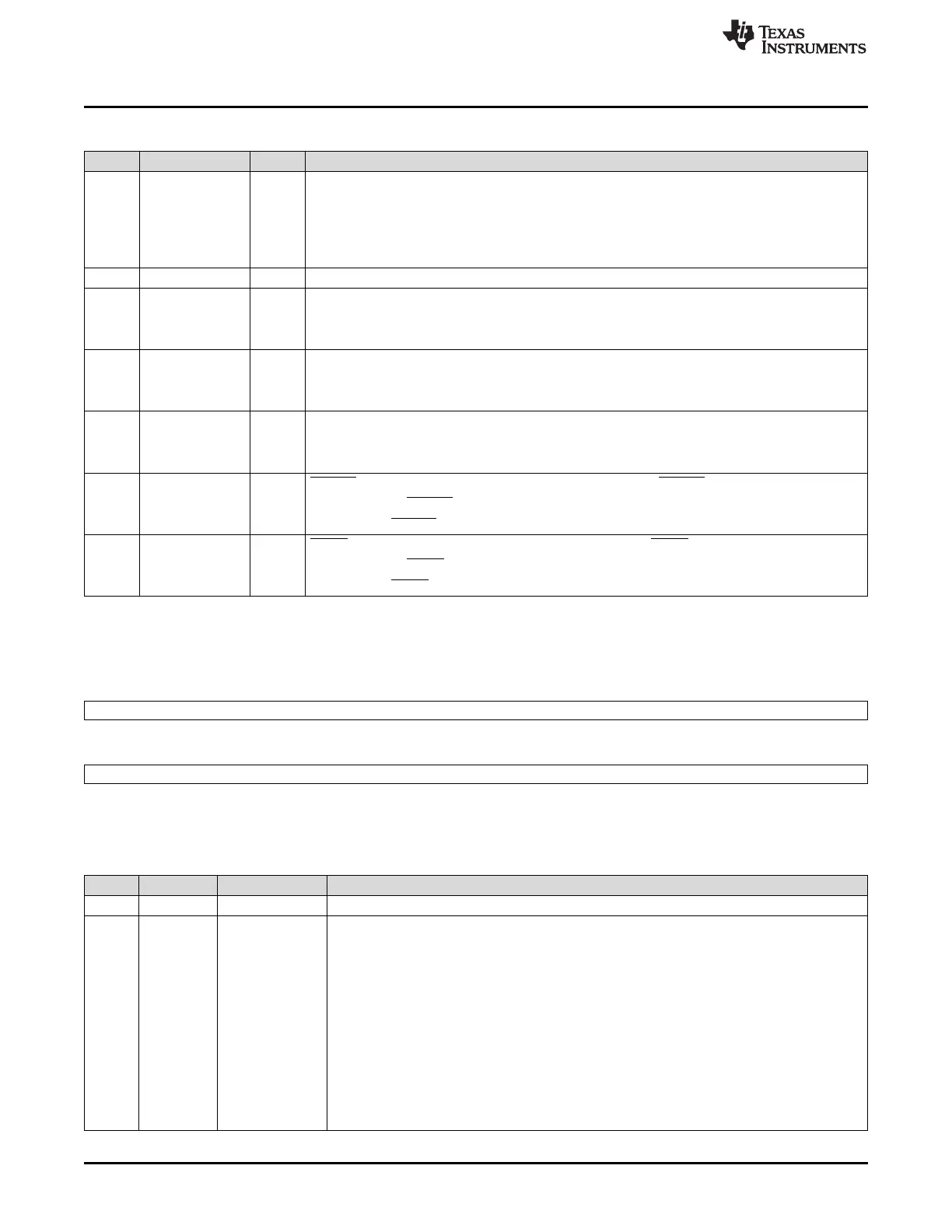

Table 28-22. SPI Pin Control Register 8 (SPIPC8) Field Descriptions (continued)

Bit Field Value Description

23-16 SIMOPSEL SPISIMOx pull select. This bit selects the type of pull logic at the SPISIMOx pin.

Note: Bit 10 or bit 16 can be used to set pull-select for SPISOMI0. If a 32-bit write is

performed, bit 10 will have priority over bit 16.

0 Pull down on the SPISIMOx pin.

1 Pull up on the SPISIMOx pin.

15-12 Reserved 0 Reads return 0. Writes have no effect.

11 SOMIPSEL0 SOMI pull select. This bit selects the type of pull logic at the SOMI pin.

0 Pull down on the SPISOMI pin.

1 Pull up on the SPISOMI pin.

10 SIMOPSEL0 SPISIMO pull select. This bit selects the type of pull logic at the SPISIMO pin.

0 Pull down on the SPISIMO pin.

1 Pull up on the SPISIMO pin.

9 CLKPSEL SPICLK pull select. This bit selects the type of pull logic at the SPICLK pin.

0 Pull down on the SPICLK pin.

1 Pull up on the SPICLK pin.

8 ENAPSEL SPIENA pull select. This bit selects the type of pull logic at the SPIENA pin.

0 Pull down on the SPIENA pin.

1 Pull up on the SPIENA pin.

7-0 SCSPSEL SPICS pull select. This bit selects the type of pull logic at the SPICS pin.

0 Pull down on the SPICS pin.

1 Pull up on the SPICS pin.

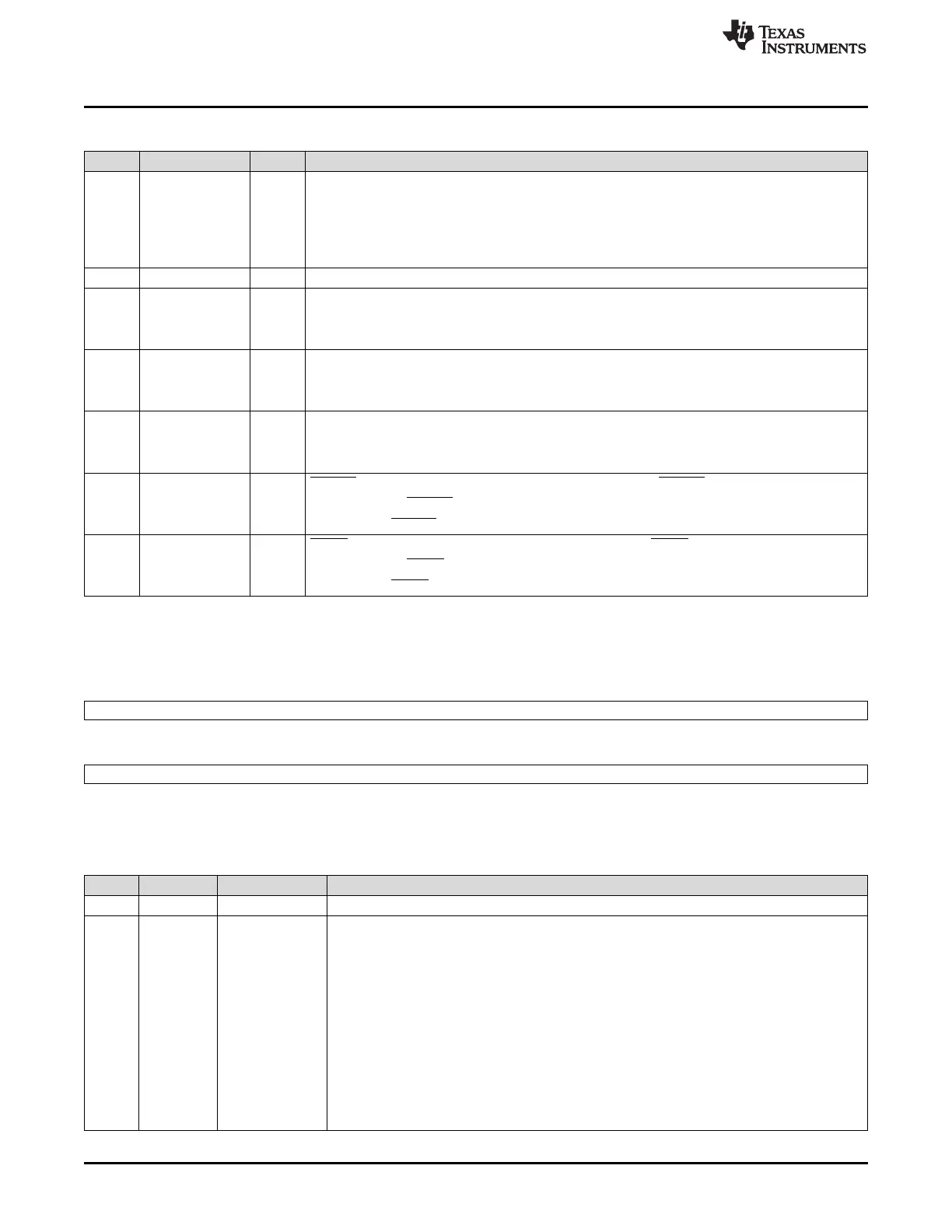

28.3.15 SPI Transmit Data Register 0 (SPIDAT0)

Figure 28-46. SPI Transmit Data Register 0 (SPIDAT0) [offset = 38h]

31 16

Reserved

R-0

15 0

TXDATA

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 28-23. SPI Transmit Data Register 0 (SPIDAT0) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-0 TXDATA 0-FFFFh SPI transmit data. When written, these bits will be copied to the shift register if it is empty. If the

shift register is not empty, TXBUF holds the written data. SPIEN (SPICGR1[24]) must be set to

1 before this register can be written to. Writing a 0 to the SPIEN register forces the lower 16 bits

of the SPIDAT0 to 0x00.

Note: When this register is read, the contents TXBUF, which holds the latest written data,

will be returned.

Note: Regardless of character length, the transmit word should be right-justified before

writing to the SPIDAT1 register.

Note: The default data format control register for SPIDAT0 is SPIFMT0. However, it is

possible to reprogram the DFSEL[1:0] fields of SPIDAT1 before using SPIDAT0, to select

a different SPIFMTx register.

Note: It is highly recommended to use SPIDAT1 register, SPIDAT0 is supported for

compatibility reasons.

Loading...

Loading...