www.ti.com

HTU Control Registers

1163

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer Transfer Unit (HTU) Module

24.4.17 BER Interrupt Flag Register (HTU BERINTFL)

A bus error interrupt results due to an address error or a timeout condition on the main memory access. A

bus error will stop the frame transfer. Please see Section 24.2.3.

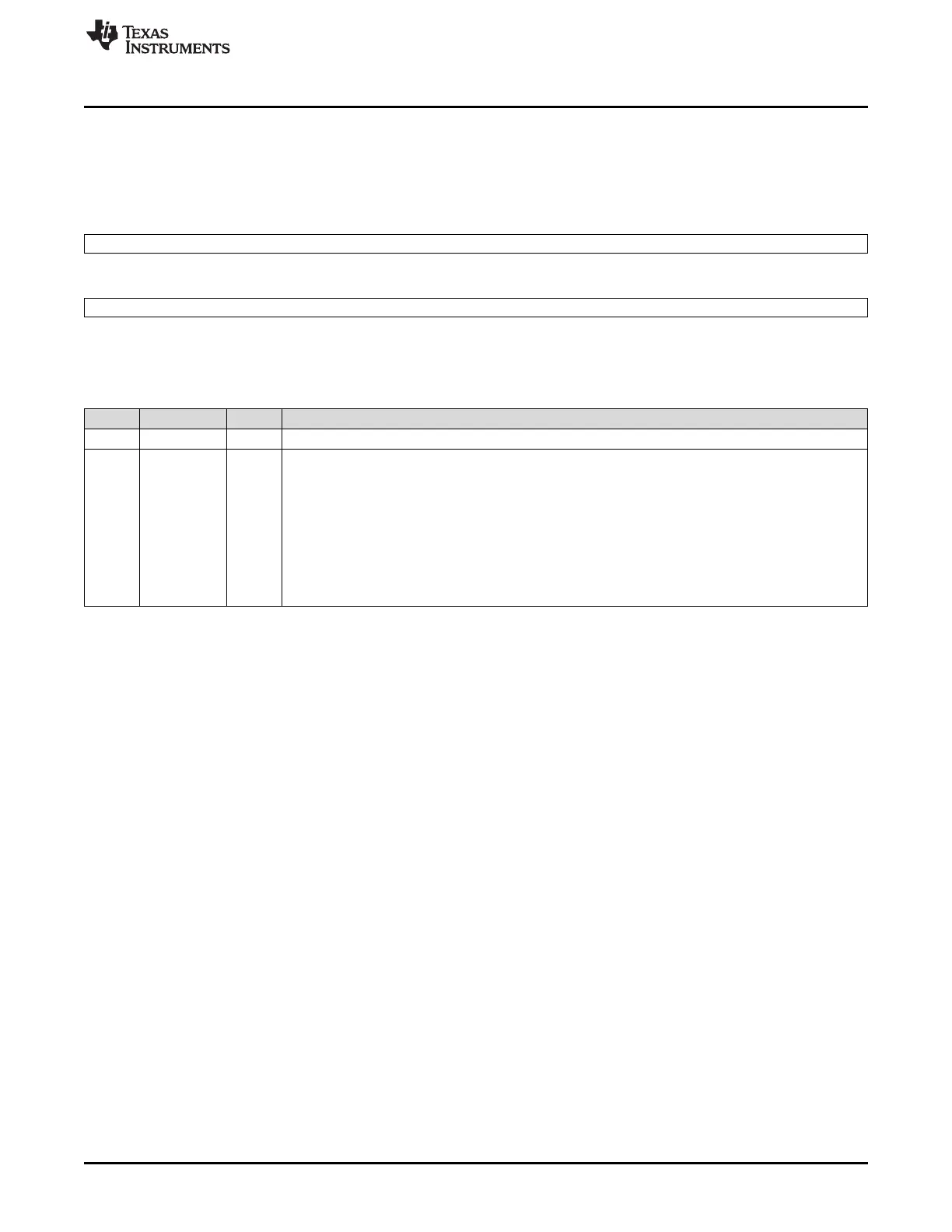

Figure 24-30. BER Interrupt Flag Register (HTU BERINTFL) [offset = 48h]

31 16

Reserved

R-0

15 0

BERINTFL

R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 in privilege mode to clear the bit; -n = value after reset

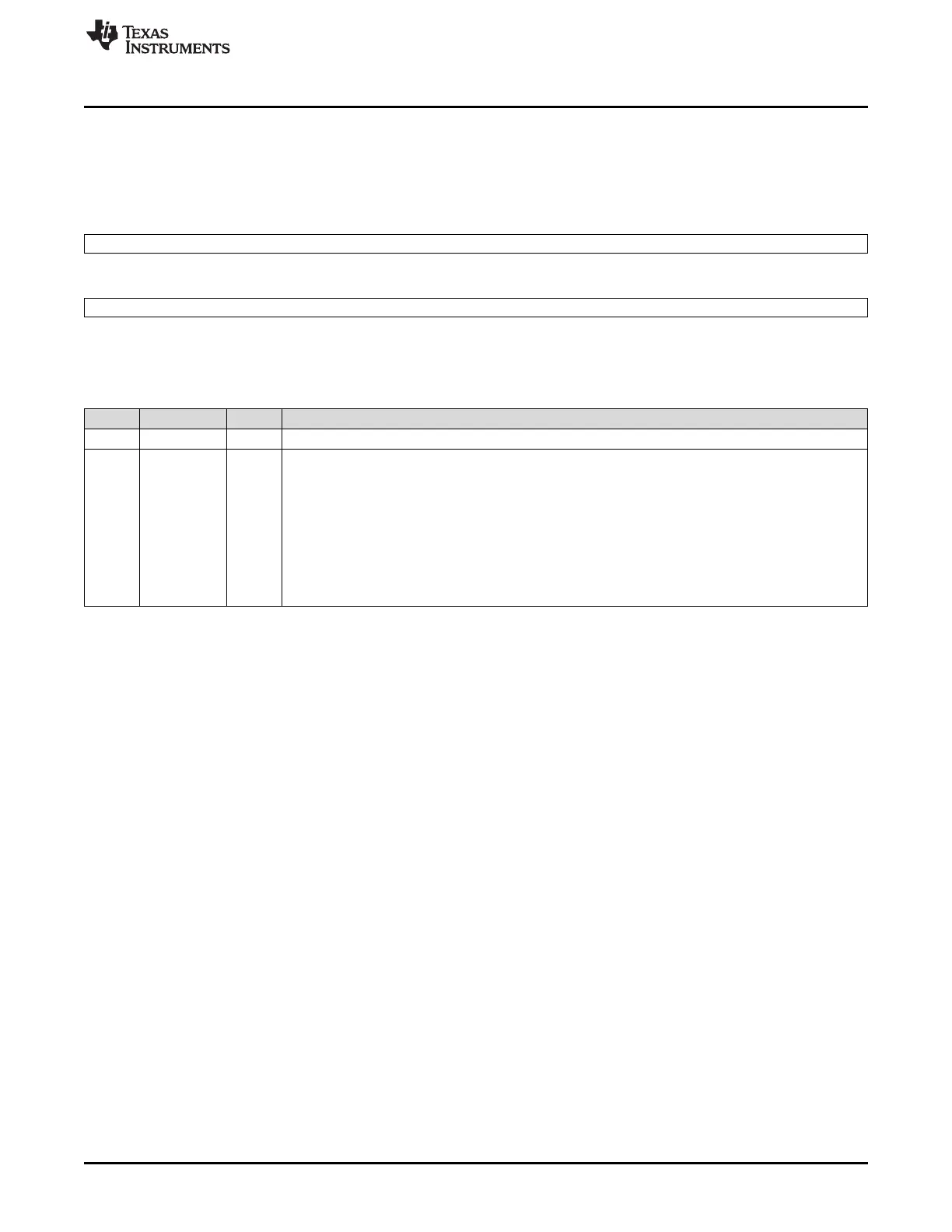

Table 24-30. BER Interrupt Flag Register (HTU BERINTFL) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-0 BERINTFL Bus Error Interrupt Flags

0 No bus error condition is detected. Writing a 0 has no effect.

1 If bit (2*x) is set, then a BER interrupt is pending on CP A of DCP x.

If bit (2*x+1) is set, then a BER interrupt is pending on CP B of DCP x.

The state of the flag bit can be polled even if BERINTENA is cleared.

• Reading BERINTFL will not clear the flags or

• Reading from INTOFFx in case of a BER interrupt clears the corresponding flag or

• Writing a 1 clears the corresponding flag.

Loading...

Loading...