www.ti.com

ESM Control Registers

573

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Error Signaling Module (ESM)

16.4.13 ESM Low-Time Counter Register (ESMLTCR)

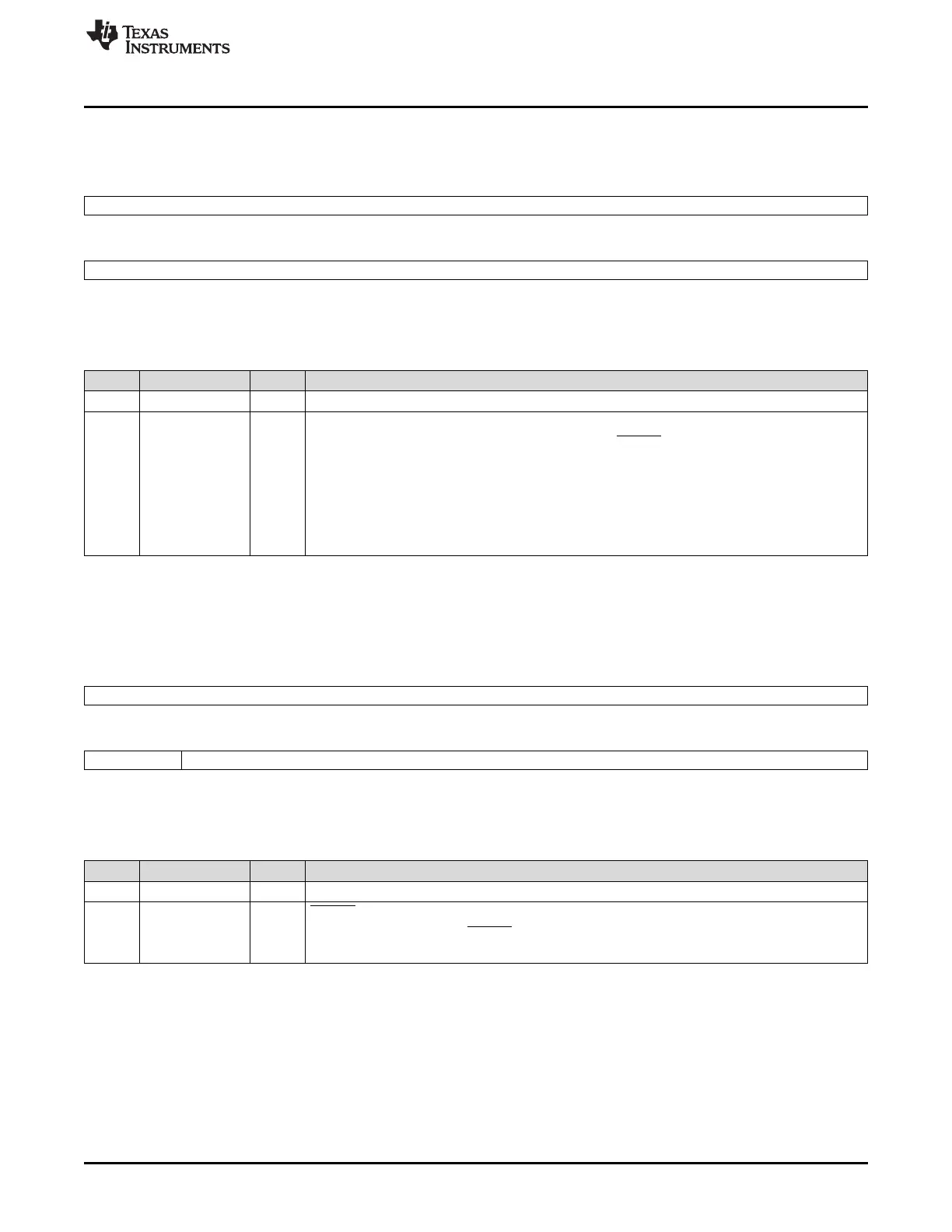

Figure 16-23. ESM Low-Time Counter Register (ESMLTCR) [offset = 30h]

31 16

Reserved

R-0

15 0

LTC

R-3FFFh

LEGEND: R = Read only; -n = value after reset

Table 16-15. ESM Low-Time Counter Register (ESMLTCR) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-0 LTC ERROR Pin Low-Time Counter

16-bit pre-loadable down-counter to control low-time of ERROR pin. The low-time counter is

triggered by the peripheral clock (VCLK).

Note: Low time counter is set to the default pre-load value of the ESMLTCPR in the following

cases:

1. Reset (power on reset or warm reset)

2. An error occurs

3. User forces an error

16.4.14 ESM Low-Time Counter Preload Register (ESMLTCPR)

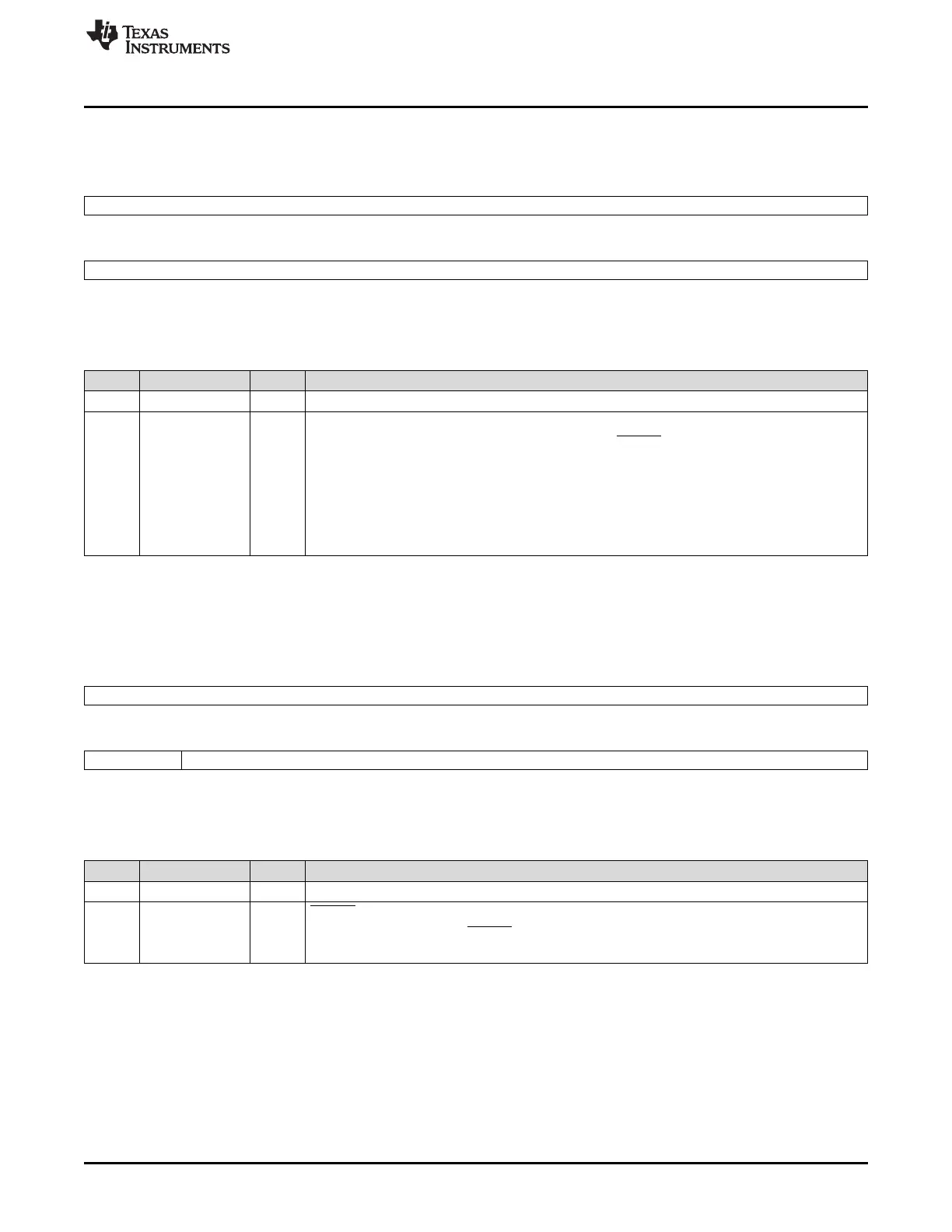

Figure 16-24. ESM Low-Time Counter Preload Register (ESMLTCPR) [offset = 34h]

31 16

Reserved

R-0

15 14 13 0

LTCP LTCP

R/WP-0 R-3FFFh

LEGEND: R/W = Read/Write; R = Read; WP = Write in privileged mode only; -n = value after reset

Table 16-16. ESM Low-Time Counter Preload Register (ESMLTCPR) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-0 LTCP ERROR Pin Low-Time Counter Pre-load Value

16-bit pre-load value for the ERROR pin low-time counter.

Note: Only LTCP.15 and LTCP.14 are configurable (privileged mode write).

Loading...

Loading...