www.ti.com

DCAN Control Registers

1469

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.13 Auto-Bus-On Time Register (DCAN ABOTR)

NOTE: On write access to the CAN Control register while Auto-Bus-On timer is running, the Auto-

Bus-On procedure will be aborted.

During Debug/Suspend mode, running Auto-Bus-On timer will be paused.

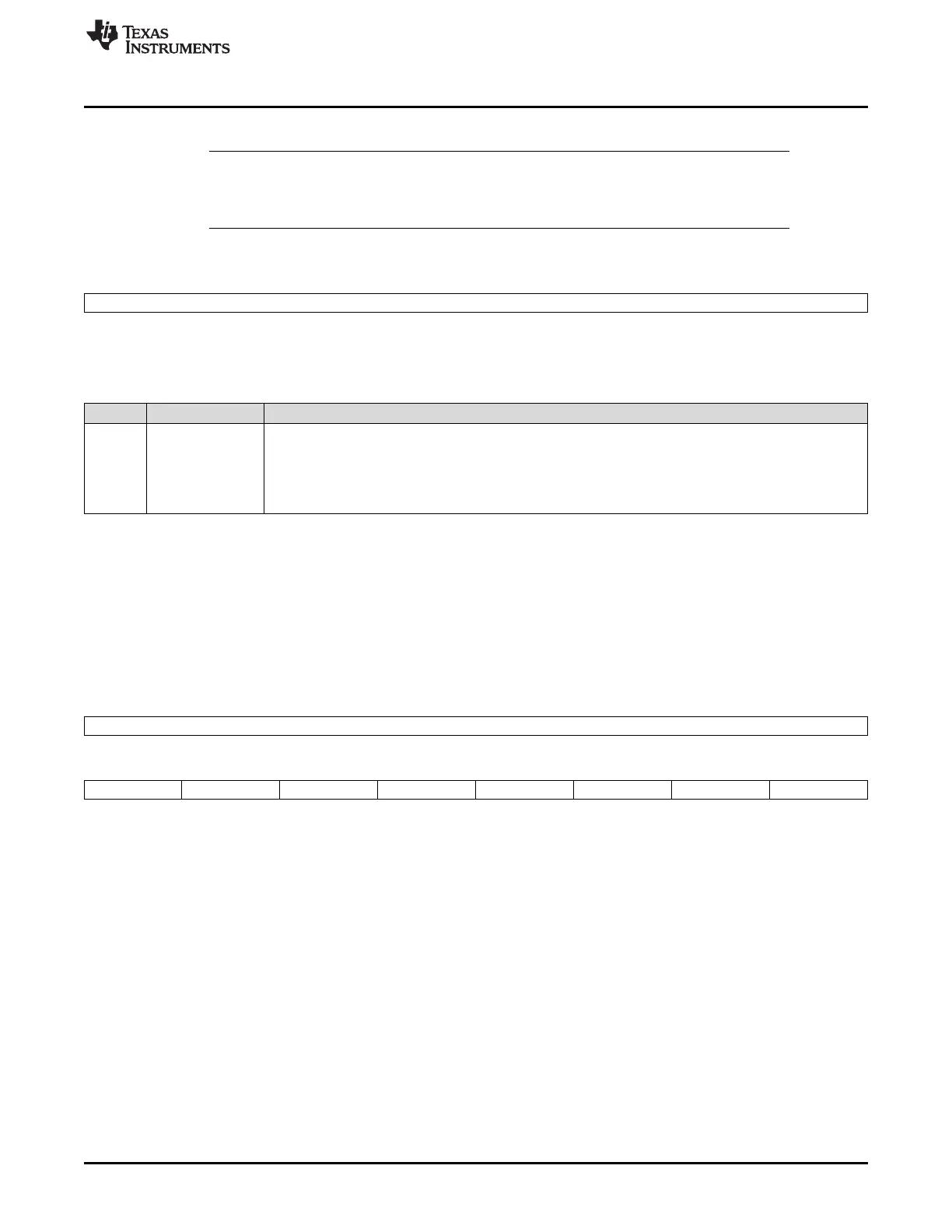

Figure 27-32. Auto-Bus-On Time Register (DCAN ABOTR) [offset = 80h]

31 0

ABO_TIME

R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

Table 27-19. Auto-Bus-On Time Register (DCAN ABOTR) Field Descriptions

Bit Field Description

31-0 ABO_TIME Number of VBUS clock cycles before a Bus-Off recovery sequence is started by clearing the Init bit. This

function has to be enabled by setting bit ABO in CAN Control Register.

The Auto-Bus-On timer is realized by a 32-bit counter that starts to count down to 0 when the module goes

Bus-Off.

The counter will be reloaded with the preload value of the ABO_TIME register after this phase.

27.17.14 Transmission Request X Register (DCAN TXRQ X)

With the Transmission Request X Register, the CPU can detect if one or more bits in the different

Transmission Request Registers are set. Each register bit represents a group of eight message objects. If

at least one of the TxRqst bits of these message objects are set, the corresponding bit in the

Transmission Request X Register will be set.

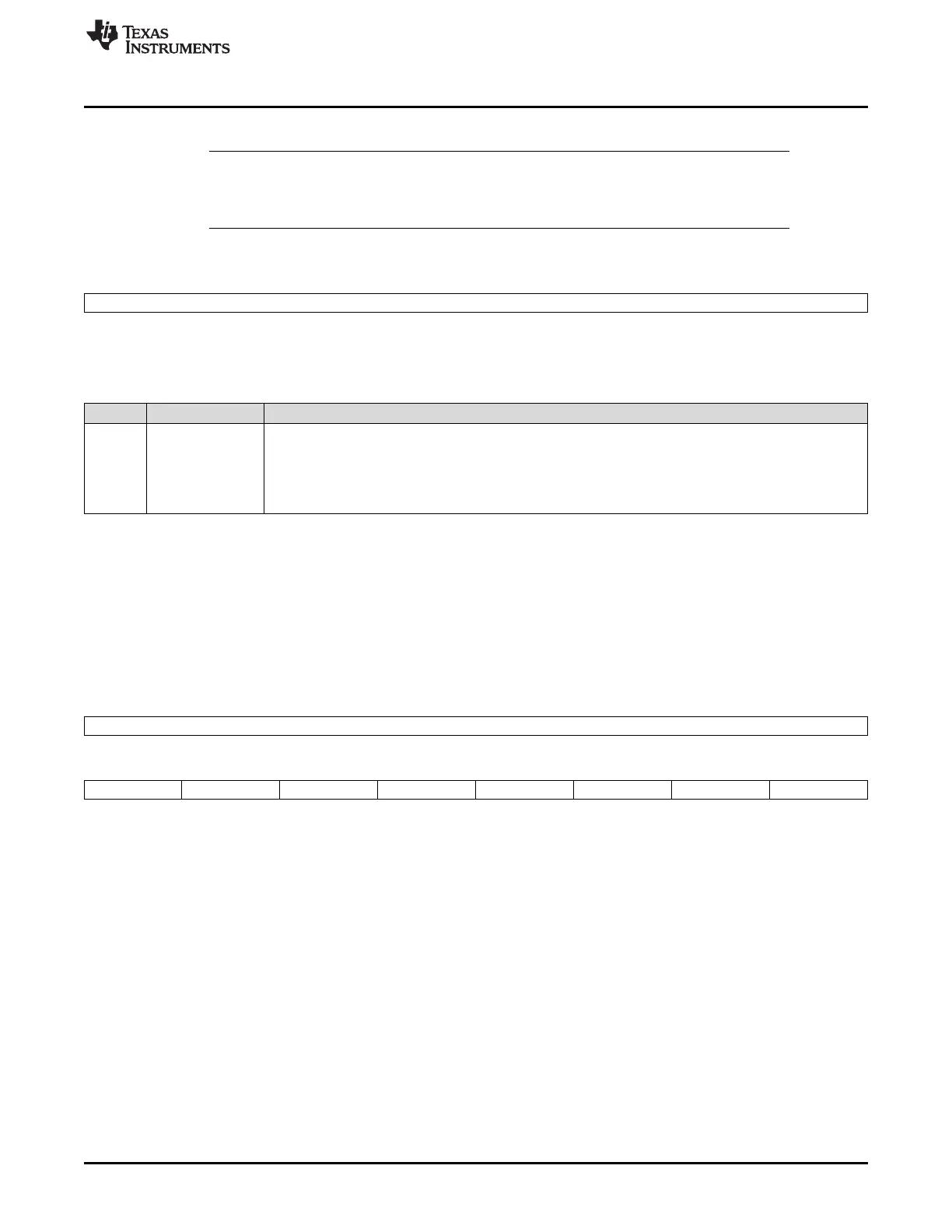

Figure 27-33. Transmission Request X Register (DCAN TXRQ X) [offset = 84h]

31 16

Reserved

R-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TxRqstReg8 TxRqstReg7 TxRqstReg6 TxRqstReg5 TxRqstReg4 TxRqstReg3 TxRqstReg2 TxRqstReg1

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

Example 1

Bit 0 of the Transmission Request X Register represents byte 0 of the Transmission Request 1 Register. If

one or more bits in this byte are set, bit 0 of the Transmission Request X Register will be set.

Loading...

Loading...