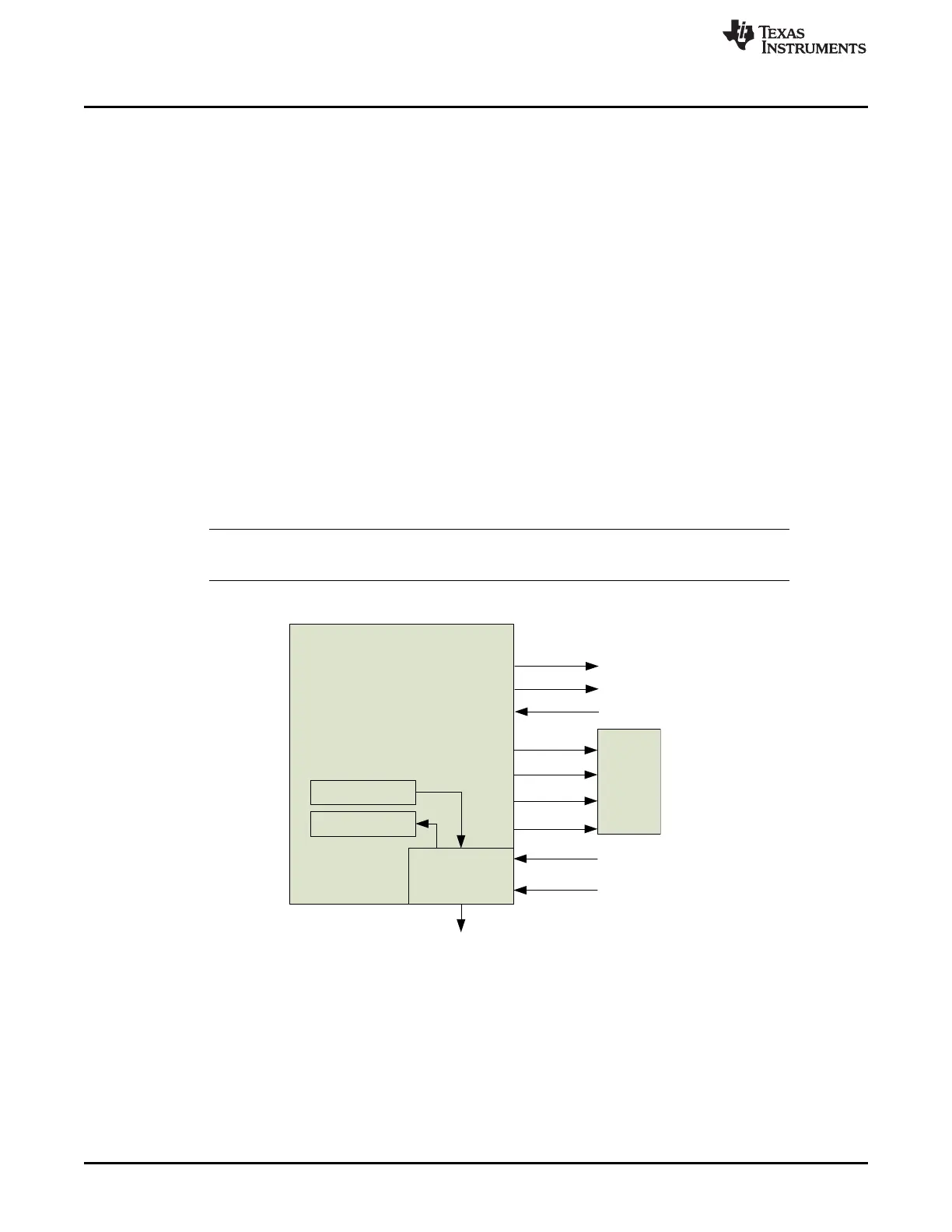

PortA

Addr.

Addr. Parity

Controls

Control Parity

Response

Response Parity

Parity Checkers

DMA

DMA_TER_ERR

(to ESM)

PortB

Addr.

Controls

Response

TERECTRL

TEROFFSET

TER_EN

NOTE: Only PortA supports transaction parity

Ext.

Parity

Checkers

Module Operation

www.ti.com

720

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

20.2.19 Transaction Errors

DMA generates parity for all transactions and checks parity for responses to the transactions. Note that

this feature is distinct from the ECC checking for the Control Packet RAM.

If a parity error is detected in these transactions and TER_EN bit in TERECTRL register is enabled, DMA

will stop processing the current channel at the arbitration boundary and will update TER_ERR flag. The

offset of the channel during which the parity failure was detected will get captured in the TERROFFSET

register. Also, the error is indicated to the ESM module. This is shown in Figure 20-18.

Since the channel stops due to an error and likely the peripheral and the DMA are out of synchronization,

it is recommended to follow the sequence below to resume the channel:

1. Read the TEROFFSET register to find the channel number causing the transaction error. The register

automatically clears to 0 once read.

2. Clear the TER_ERR flag by writing 1 to the flag.

3. Disable the peripheral that triggered the DMA event.

4. Reinitialize the control packet. Note that this does not change the channel's HWCHEN bit.

5. Re-enable the peripheral to trigger the DMA event.

6. Re-enable the DMA channel (which was previously cleared by the DMA logic due to the error).

In certain cases, it is possible that DMA sets the TER_ERR flag without updating the TEROFFSET

register. This occurs due to parity errors when no channels are active. The recovery sequence in this case

is to clear the TER_ERR flag.

NOTE: Handling of a parity error at a system level may require additional operations that are not

detailed here.

Figure 20-18. DMA Transaction Parity

Loading...

Loading...