CRC Control Registers

www.ti.com

650

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Cyclic Redundancy Check (CRC) Controller Module

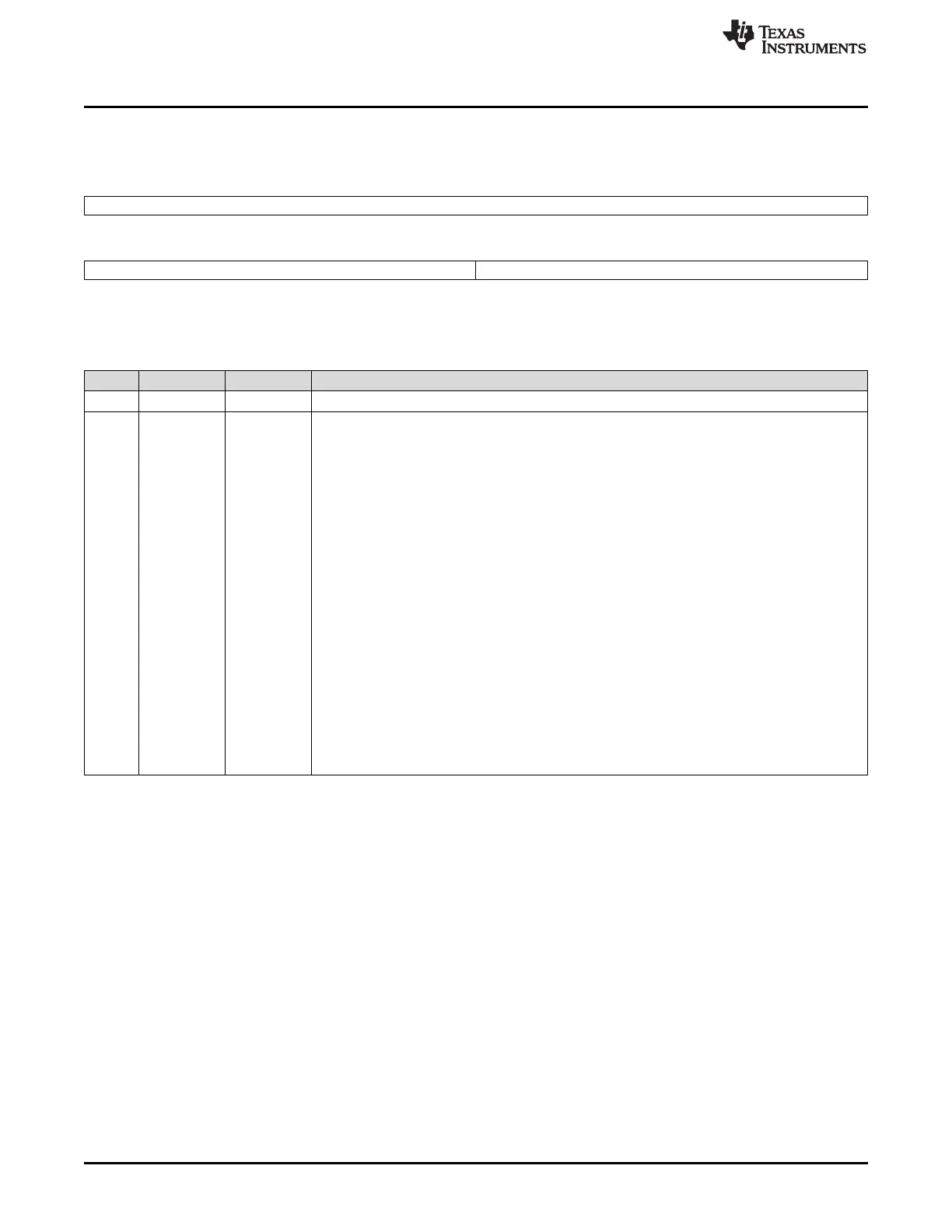

18.4.7 CRC Interrupt Offset (CRC_INT_OFFSET_REG)

Figure 18-15. CRC Interrupt Offset (CRC_INT_OFFSET_REG) [offset = 30h]

31 16

Reserved

R-0

15 8 7 0

Reserved OFSTREG

R-0 R-0

LEGEND: R = Read only; -n = value after reset

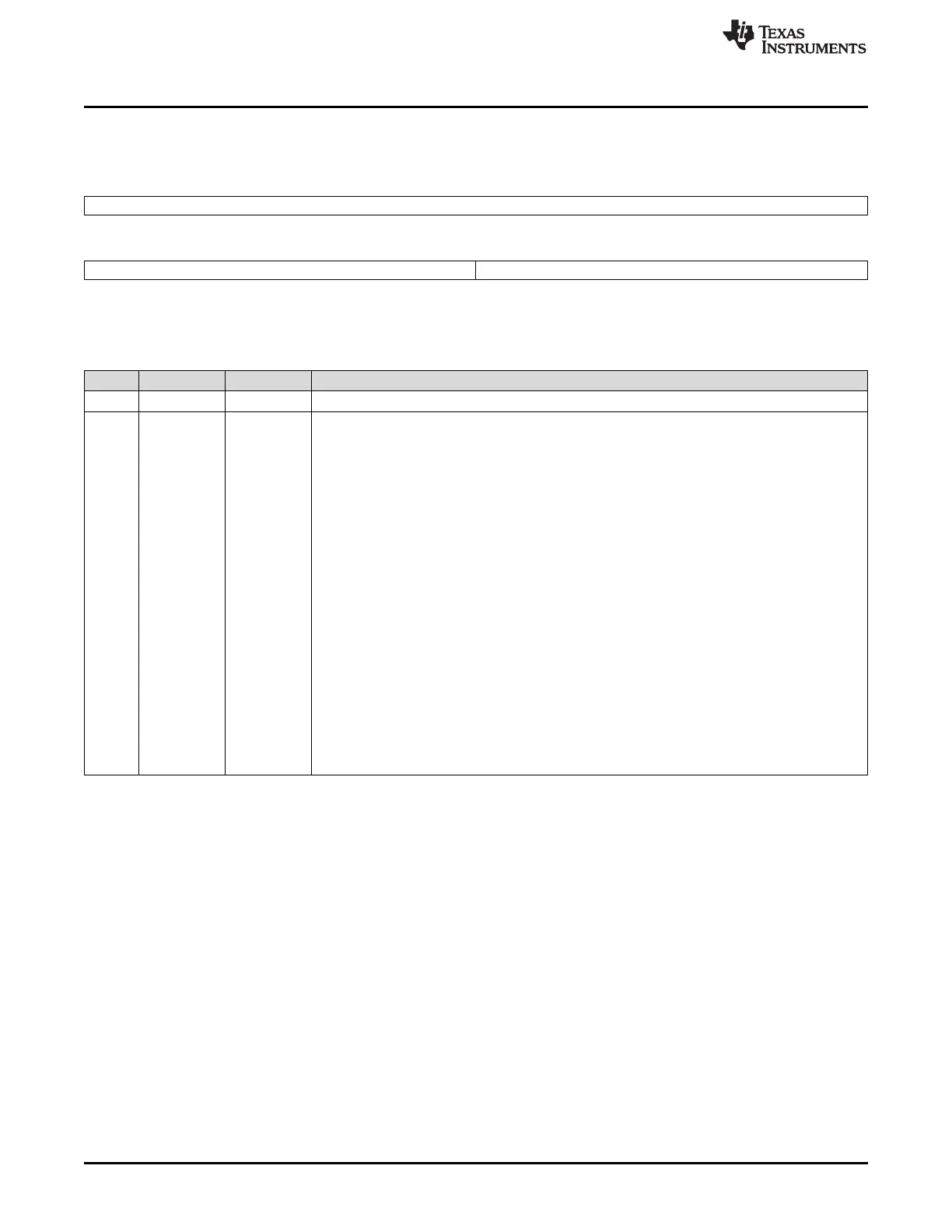

Table 18-11. CRC Interrupt Offset (CRC_INT_OFFSET_REG) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 OFSTREG CRC Interrupt Offset. This register indicates the highest priority pending interrupt vector address.

Reading the offset register automatically clears the respective interrupt flag.

0 Phantom

1h Ch1 CRC Fail

2h Ch2 CRC Fail

3h-8h Reserved

9h Ch1 Compression Complete

Ah Ch2 Compression Complete

Bh-10h Reserved

11h Ch1 Overrun

12h Ch2 Overrun

13h-18h Reserved

19h Ch1 Underrun

1Ah Ch2 Underrun

1Bh-20h Reserved

21h Ch1 Timeout

22h Ch2 Timeout

23h-FFh Reserved

Loading...

Loading...