www.ti.com

POM Control Registers

383

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

F021 Level 2 Flash Module Controller (L2FMC)

7.11 POM Control Registers

This section details the POM module registers listed in Table 7-48.

The POM module control registers can only be read and/or written while in privileged or debug mode.

Each register begins on a word boundary. All registers are 32-bit, 16-bit and 8-bit accessible. The start

address of the POM module is FFA0 4000h.

Table 7-48. POM Control Registers

Offset Acronym Register Description Section

00h POMGLBCTRL POM Global Control Register Section 7.11.1

04h POM_REVID POM Revision ID Register Section 7.11.2

0Ch POMFLG POM Flag Register Section 7.11.3

200h, 210h, ... PROMPROGSTARTx POM Region Start Address Register Section 7.11.4

204h, 214h,... POMOVLSTARTx POM Overlay Start Address Register Section 7.11.5

208h, 218h,... POMREGSIZEx POM Region Size Register Section 7.11.6

7.11.1 POM Global Control Register (POMGLBCTRL)

Contains enable control for the POM module.

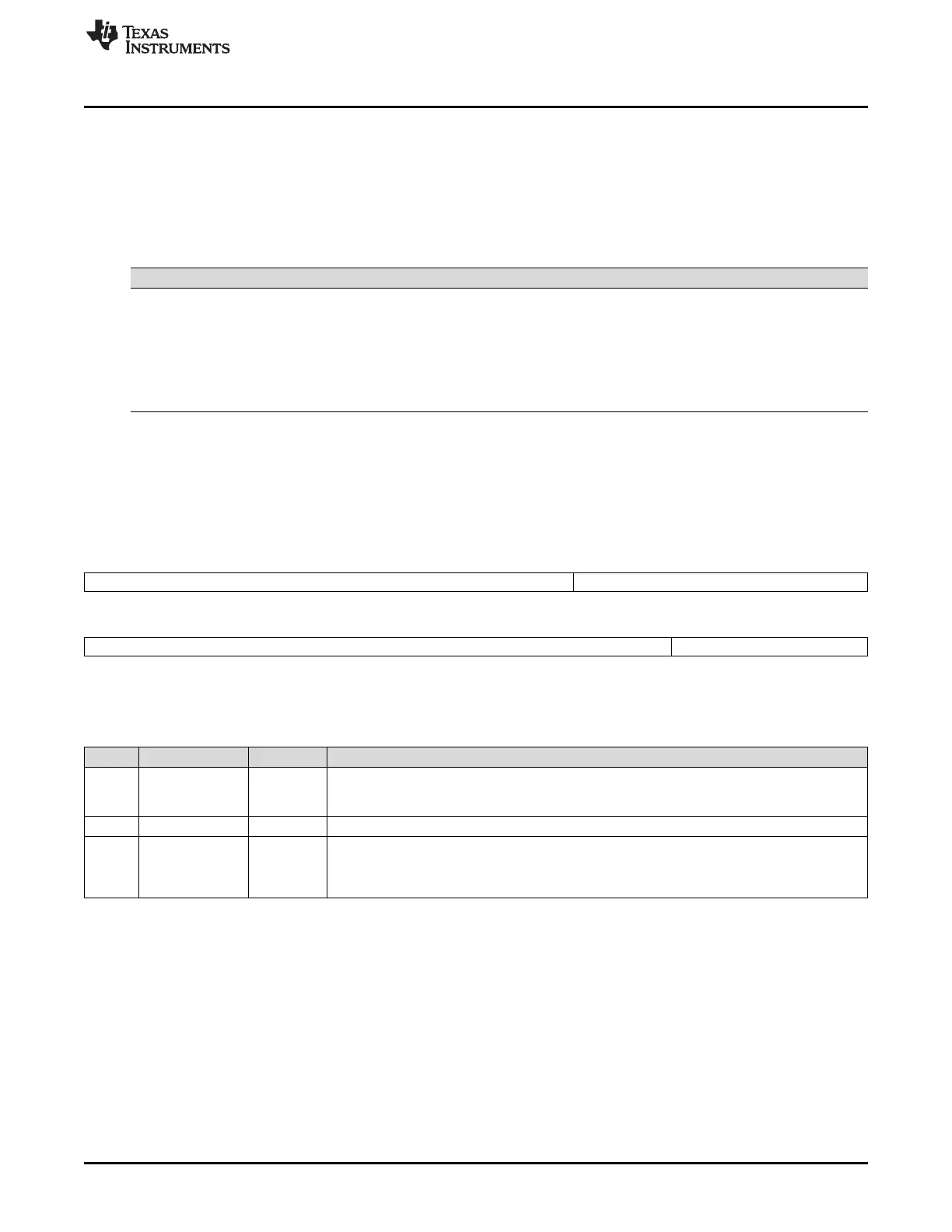

Figure 7-46. POM Global Control Register (POMGLBCTRL) (offset = 00h)

31 22 21 16

OTADDR Reserved

R/WP-01 1000 0000 R-0

15 4 3 0

Reserved ON_OFF

R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege Mode; -n = value after reset

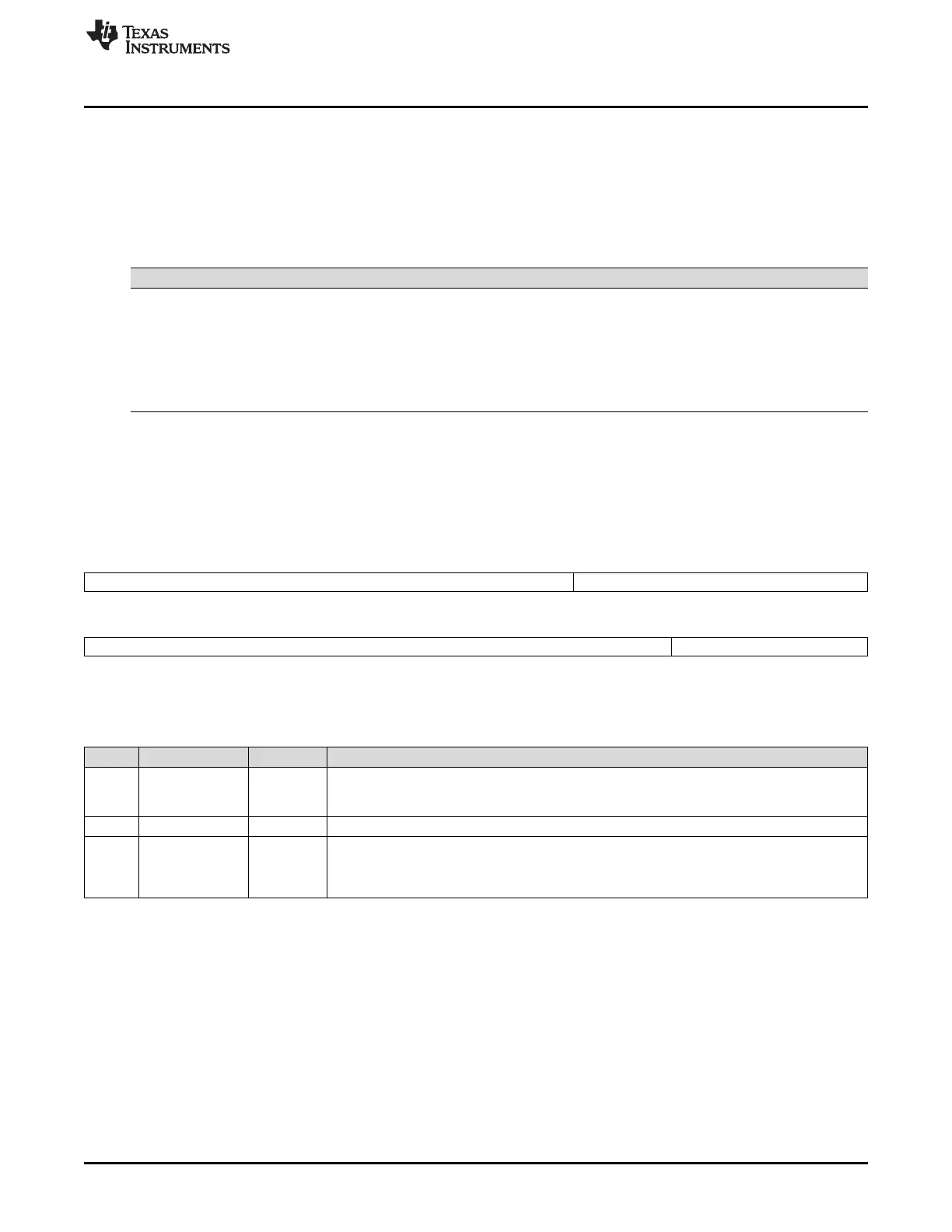

Table 7-49. POM Global Control Register (POMGLBCTRL) Field Descriptions

Bit Field Value Description

31-22 OTADDR Overlay Target Address. These bits determine the upper address bits of the remapped address.

Writing a different value to this bitfield will steer the access to a different location in the 4GB

address space. Care has to be taken that the value written represents actual memory.

21-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 ON_OFF POM enable

except Ah POM is disabled.

Ah POM is enabled.

Loading...

Loading...