EPC Control Registers

www.ti.com

492

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Error Profiling Controller (EPC)

12.4.4 EPC Error Status Register (EPCERRSTAT)

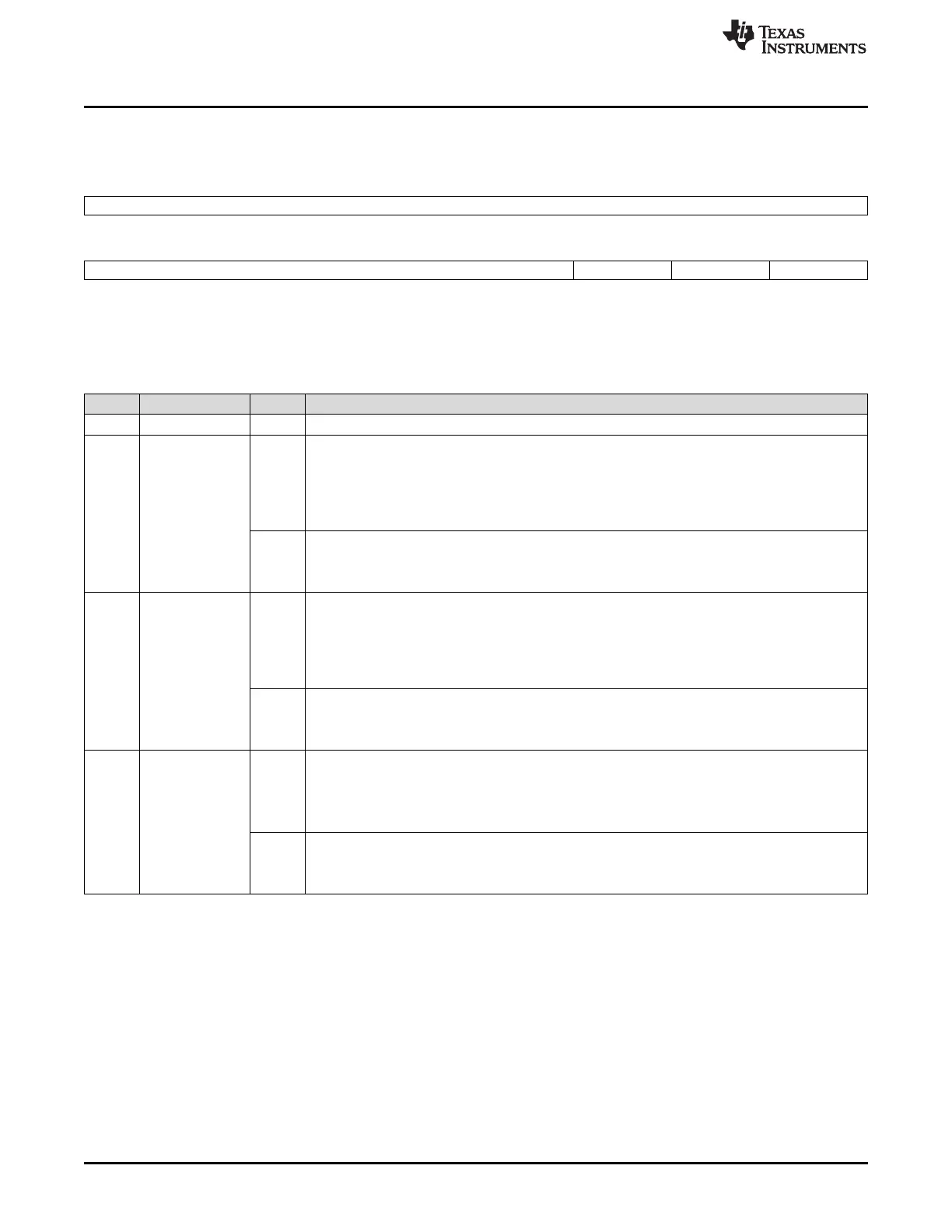

Figure 12-5. EPC Error Status Register (EPCERRSTAT) (offset = 0Ch)

31 16

Reserved

R-0

15 3 2 1 0

Reserved CAM_FULL BUS_ERR CAM_OVFLW

R-0 R/W1CP-0 R/W1CP-0 R/W1CP-0

LEGEND: R/W = Read/Write; R = Read only; W1CP = Write 1 to clear in privilege mode only; -n = value after asynchronous reset by

power-on reset

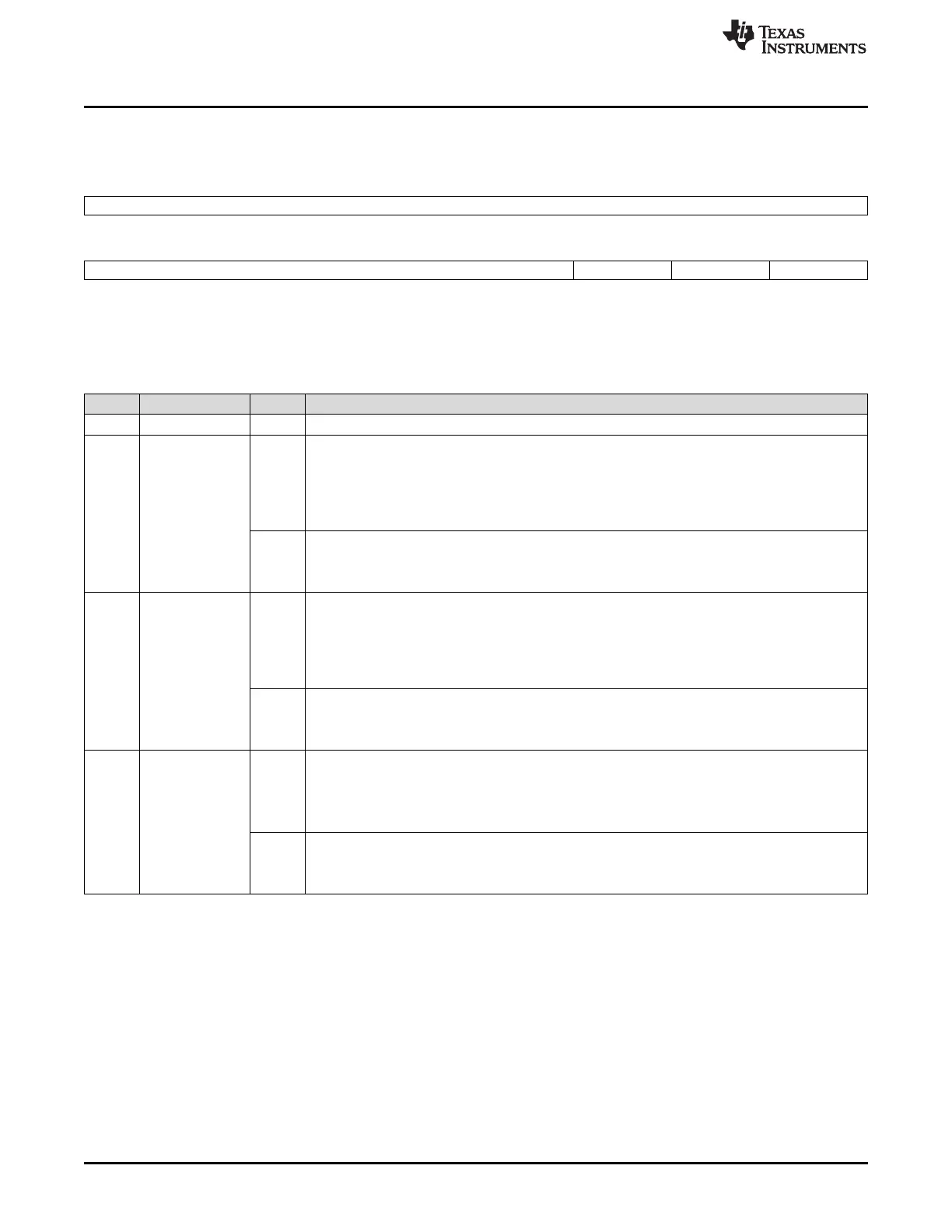

Table 12-5. EPC Error Status Register (EPCERRSTAT) Field Descriptions

Bit Field Value Description

31-3 Reserved 0 Reserved. Reads return 0.

2 CAM_FULL CAM full status bit. This bit is set when CAM has no more available index available to accept new

correctable address.

Read:

0 CAM is not full.

1 CAM is full.

Write in Privilege:

0 No effect.

1 Clear this flag bit.

1 BUS_ERR MMR interface bus error status bit. This bit is set if MMR interface receives unsupported bus

commands like ReadLink-WriteConditional.

Read:

0 No MMR bus error.

1 MMR unsupported bus command is detected.

Write in Privilege:

0 No effect.

1 Clear this flag bit.

0 CAM_OVFLW CAM overflow status bit. CAM is full and there is another correctable address arrives.

Read:

0 No CAM overflow.

1 CAM overflow is detected.

Write in Privilege:

0 No effect.

1 Clear this flag bit.

Loading...

Loading...