ADC Registers

www.ti.com

946

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

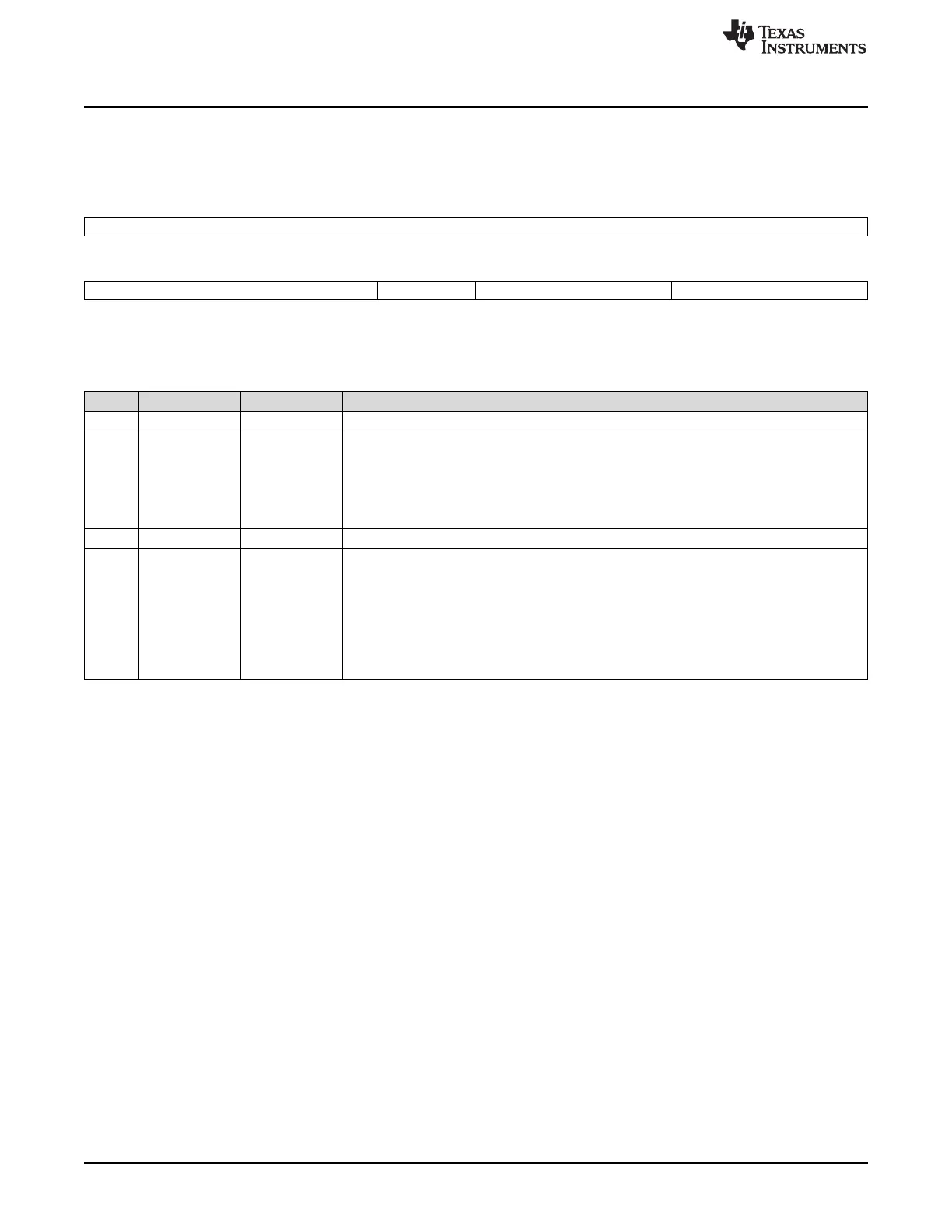

22.3.66 ADC Parity Control Register (ADPARCR)

ADC Parity Control Register (ADPARCR) is shown in Figure 22-97 and described in Table 22-72.

Figure 22-97. ADC Parity Control Register (ADPARCR) [offset = 180h]

31 16

Reserved

R-0

15 9 8 7 4 3 0

Reserved TEST Reserved PARITY_ENA

R-0 R/WP-0 R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

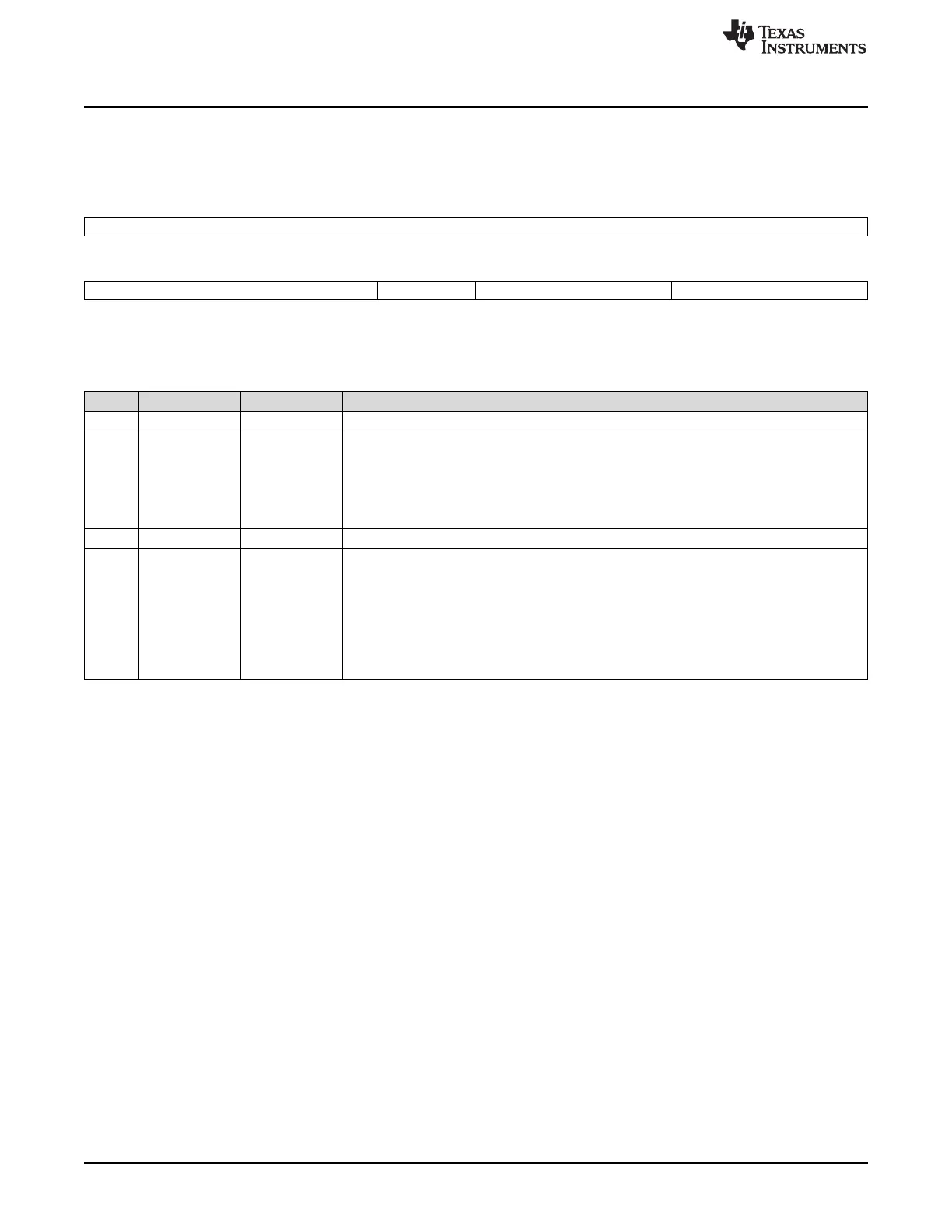

Table 22-72. ADC Parity Control Register (ADPARCR) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reads return 0. Writes have no effect.

8 TEST This bit maps the parity bits into the ADC results' RAM frame so that the application can

access them.

Any operation mode read, privileged mode write:

0 The parity bits are not memory-mapped.

1 The parity bits are memory-mapped.

7-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 PARITY_ENA Enable parity checking. These bits enable the parity check on read operations and the parity

calculation on write operations to the ADC results memory.

If parity checking is enabled and a parity error is detected the ADC module sends a parity

error signal to the System module.

Any operation mode read, privileged mode write:

5h Parity check is disabled.

All other values Parity check is enabled.

Loading...

Loading...